## GaAs MMIC Reliability Assurance Guideline

## for Space Applications

Sammy Kayali

Jet Propulsion Laboratory

George Ponchak

NASA Lewis Research Center

Roland Shaw

Shason Microwave Corporation

Editors

December 15, 1996

National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

The research described in this publication was carried out by the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration.

Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States Government or the Jet Propulsion Laboratory, California Institute of Technology.

#### **Preface**

This document was conceived in response to comments by various industry representatives lamenting the lack of an industry-accepted method for MMIC qualification. A low-level effort to address this problem was initiated in the summer of 1992 by individuals at the Jet Propulsion Laboratory, NASA Lewis Research Center, and NASA Johnson Space Center. These efforts were combined in July 1993 to form the MMIC Reliability Assurance Working Group, which gained the support of NASA Headquarters, Code Q.

The original concept was an official government-sponsored MMIC qualification specification describing all the required test and evaluation procedures performed by the manufacturer. This approach was presented to industry representatives at the first MMIC Qualification Workshop held at NASA Lewis Research Center in Cleveland, Ohio, in September 1993. At this meeting, various users and suppliers of MMIC devices expressed their strong desire to avoid government specifications and requested a document that would be an educational tool. The format was envisioned to be a source book of GaAs MMIC reliability and design methodology techniques useful in developing a qualification plan for the production and use of GaAs MMIC in space applications. The workshop attendees concluded that the title of the document should be GaAs MMIC Reliability Assurance Guideline for Space Applications. The guide was developed to be a practical application of industry-accepted reliability assurance practices used for the specification, manufacture, qualification, and procurement of GaAs-based MMICs.

The text contains background material on and discussion of the tests, screens, and evaluations normally conducted on MMIC devices prior to approval for use in high-reliability applications. The information is focused on the needs of the engineer, the program-level manager, and the purchaser, with the emphasis on the common approaches to GaAs MMIC reliability and qualification methodologies used and accepted in the industry.

Background information is provided on the materials, design methodology, test techniques, environment effects, common failure mechanisms, and fabrication processes—information needed to structure an effective qualification plan for the specific application required. Using this information as a common reference point, the user and the manufacturer can discuss trade-offs and determine the value-added tests necessary to realize a cost-effective qualification plan.

The guide begins with an introduction of GaAs usage and brief summary of MMIC development history. This is followed by a reliability overview and a summary description of reliability theory. These chapters give the reader an understanding of the usage of GaAs devices in various applications and provide the background necessary to understand reliability test results and the implication of failure.

GaAs material properties and common device structures used in MMIC designs are discussed in Chapter 3. This chapter also provides general descriptions of the common processes and the various general-purpose MMIC functions and circuits. Chapter 4 provides descriptions of the common failure modes and mechanisms

affecting GaAs-based device; this information can be of great importance in developing characterization and qualification plans.

Device modeling and MMIC design methodology are discussed in Chapters 5 and 6, respectively. These chapters provide general information needed to understand the various aspects of MMIC design. The text also addresses the reliability aspects of MMIC design and provides a generalized design methodology useful to both the user and manufacturer.

Chapter 7 discusses MMIC testability and provides examples of test implementations. General test structures and process monitors employed at various stages in the manufacture of MMIC devices are also presented. Qualification methodologies are discussed in Chapter 8, along with approaches to the different aspects and levels of device development and qualification. The significance of package reliability is given in Chapter 9, together with brief descriptions of the common packaging materials and their related effects.

Finally, Chapter 10 addresses radiation effects on GaAs MMICs and discusses the radiation environments experienced during space flight and their effects on device performance.

The information contained in this document has been collected from users and manufacturers through direct interaction and collaboration. For example, the approaches to process and product acceptance, as presented in Chapter 8, were collected and compiled to present a simpler way of addressing the subject. However, this information is presented only as a suggested approach and should be modified to accommodate the different methodologies practiced by the manufacturers.

The NASA MMIC Reliability Assurance Working Group:

Sammy Kayali George Ponchak Roland Shaw

October 1996

#### Abstract

This guide is a reference for understanding the various aspects of monolithic microwave integrated circuits (MMIC). There are special emphases on the reliability aspects of MMIC devices. GaAs material properties and common device structures along with the applicable failure mechanisms are addressed in detail. MMIC design and qualification methodologies provide the reader with the means of developing suitable qualification plans. Radiation effects on GaAs devices and packaging effects on MMIC device reliability are discussed with supporting references.

## Contributors

Lisa Aucoin Raytheon Company

Charles Barnes Jet Propulsion Laboratory

Chung-Hsu Chen TRW

Y. C. Chou University of California, Irvine

Alan N. Downey NASA Lewis Research Center

Robert Ferro Aerospace Corporation

Anthony Immorlica Lockheed Martin Company

Wen Yan Jiang MPB Technologies, Inc.

Sammy Kayali Jet Propulsion Laboratory

George Ponchak NASA Lewis Research Center

Edward Rezek TRW

Robert R. NASA Lewis Research Center

Romanofsky

Luis Selva Jet Propulsion Laboratory

Roland Shaw Shason Microwave Corporation

Rainee Simons NASA Lewis Research Center

Tien Trinh TRW

## Contents

## Chapter 1. Introduction 1 (R. Shaw)

- I. Why GaAs is Used 1

- II. Hybrid and Monolithic Integrated Circuits 2

- III. Reliability and Quality Assurance 3

Additional Reading 5

#### Chapter 2. Reliability Overview 6 (R. Shaw)

- I. Failure 7

- A. Physical Failure Mechanisms 7

- B. Radiation Failure Mechanisms 8

- II. Quantifying Reliability 8

- III. GaAs Device Reliability 11

Additional Reading 14

## Chapter 3. GaAs Properties, Device Structures, and Circuits

- I. GaAs Material Properties 16 (S. Kayali)

- A. Energy Band Structure 16

- B. Mobility and Drift Velocity 18

- C. Semi-Insulating GaAs 19

- D. Crystal Defects 20

- E. Thermal Characteristics 22

References 23

Additional Reading 23

- II. Metal-Semiconductor Junctions 24 (G.E. Ponchak)

- A. Junction Physics 24

- B. Junction Characteristics 27

- C. Device Structures 30

- D. Reliability 32

Reference 33

Additional Reading 33

#### III. Metal-Semiconductor Field-Effect Transistors 34 (G.E. Ponchak)

- A. Device Physics 34

- B. Reliability 37

Additional Reading 38

#### IV. HEMTs and PHEMTs 39 (L. Aucoin)

- A. Device Physics 39

- B. Reliability 42

Reference 43

Additional Reading 43

#### V. Heterojunction Bipolar Transistors 44 (Y. C. Chou and R. Ferro)

- A. Device Structure 45

- B. Operating Principles 46

- C. Reliability 47

References 49

#### VI. PIN Diodes 51 (G. E. Ponchak)

- A. Device Physics 51

- B. Reliability 54

References 55

#### VII. Passive Elements 56 (S. Kayali and G. E. Ponchak)

- A. Resistors 56

- B. Capacitors 58

- C. Inductors 59

- D. Transmission Lines 60

- E. Via Holes 61

- F. Air Bridges 62

Reference 63

#### Additional Reading 63

#### VIII. Basic Process Description 64 (S. Kayali)

- A. Typical Ion-Implanted MESFET Process Flow 64

- B. Typical HEMT/PHEMT Process Flow 68

- C. Typical HBT Process Flow 70

Additional Reading 72

## IX. Monolithic Microwave Integrated Circuits 74 (A. N. Downey, G. E. Ponchak, and R. R. Romanofsky)

- A. General Description 74

- B. Amplifiers 76

- C. Mixers 80

- D. Oscillators 82

- E. Phase Shifters 85

References 87

## Chapter 4. Basic Failure Modes and Mechanisms 89 (S. Kayali)

#### I. General Failure Modes 89

- A. Degradation in IDSS 90

- B. Degradation in Gate Leakage Current 90

- C. Degradation in Pinch-Off Voltage 90

- D. Increase in Drain-to-Source Resistance 90

- E. Degradation in RF Performance 91

#### II. Failure Mechanisms 91

- A. Material-Interaction-Induced Failure Mechanisms 91

- B. Stress-Induced Failure Mechanisms 95

- C. Mechanically Induced Failure Mechanisms 101

- D. Environmentally Induced Failure Mechanisms 102

References 106

## Chapter 5. Device Modeling 109 (W. Y. Jiang)

- I. Types of Models 109

- II. Equivalent Circuit 110

- A. MESFET Equivalent Circuit 110

- B. HEMT Equivalent Circuit 113

#### III. Characterization and Parameter Extraction 114

- A. DC Characterization and Parameter Extraction 114

- B. RF Characterization and Parameter Extraction 114

- C. Large-Signal Characterization and Parameter Extraction 114

- D. Noise Figure Characterization 116

#### IV. Modeling Software 117

- A. Device Modeling Software 117

- B. Processing Simulation Software 118

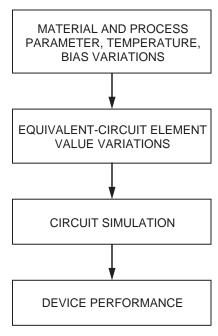

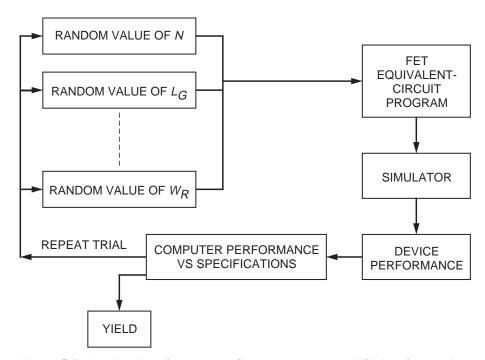

#### V. Model Sensitivity 119

- A. Sensitivity Analysis 119

- B. Temperature Effect 119

- C. DC Bias Effect 120

- D. Statistical Analysis 121

References 121

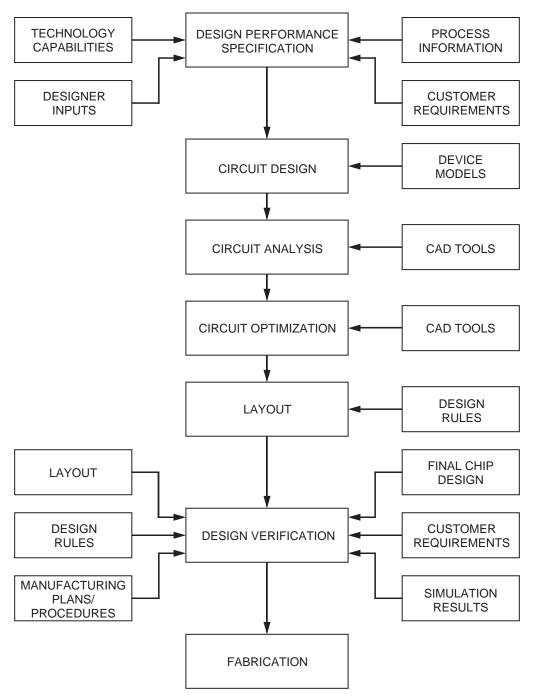

## Chapter 6. MMIC Design Methodologies and Verification 123 (C. Chen, S. Kayali, E. Rezek, and T. Trinh)

- I. Foundry Documentation 123

- II. MMIC Simulation 124

- III. MMIC Layout 125

- IV. Typical Design Methodology 126

- V. Design for Reliability and Manufacturability 127

Additional Reading 128

## Chapter 7. Testability and Test Structures 130 (R. Shaw)

#### I. Test Structures 130

- A. Technology Characterization Vehicle 130

- B. Standard Evaluation Circuits 131

#### C. Parametric Monitors 132

#### II. Testability 134

- A. Wafer-Level Testability 134

- B. MMIC-Level Tests 135

Additional Reading 136

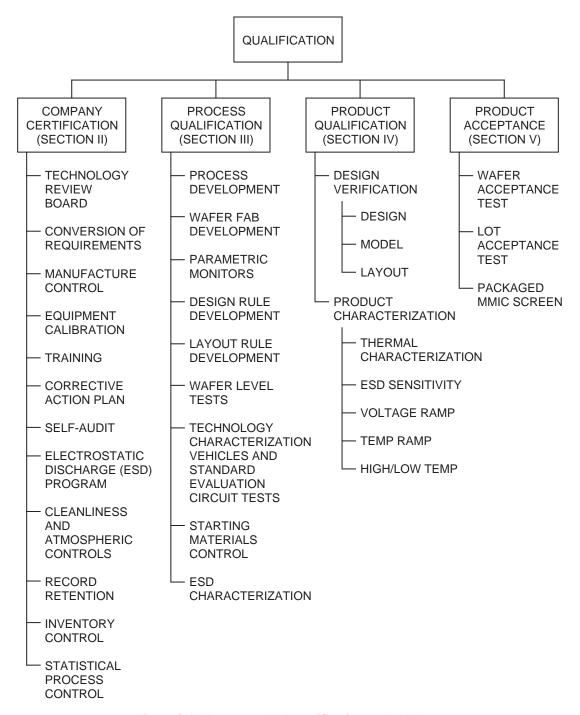

## Chapter 8. Qualification Methodologies 137 (S. Kayali, G. E. Ponchak, and R. Shaw)

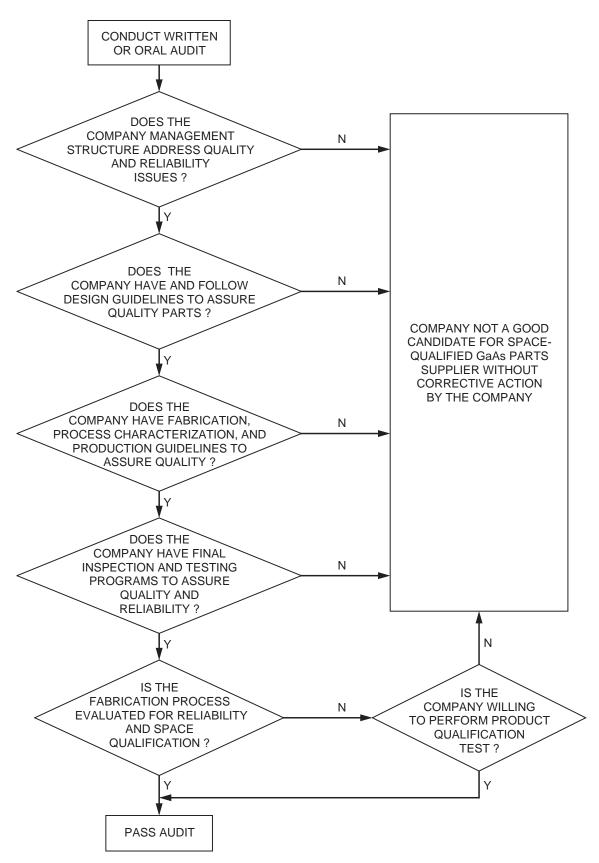

#### I. Introduction 137

#### II. Company Certification 139

- A. Technology Review Board 139

- B. Conversion of Customer Requirements 141

- C. Manufacturing Control Procedures 142

- D. Equipment Calibration and Maintenance 143

- E. Training Programs 143

- F. Corrective Action Program 143

- G. Self-Audit Program 143

- H. Electrostatic Discharge Handling Program 144

- I. Cleanliness and Atmospheric Controls 144 J. Record Retention 144

- J. Inventory Control 145

- K. Statistical Process Control 145

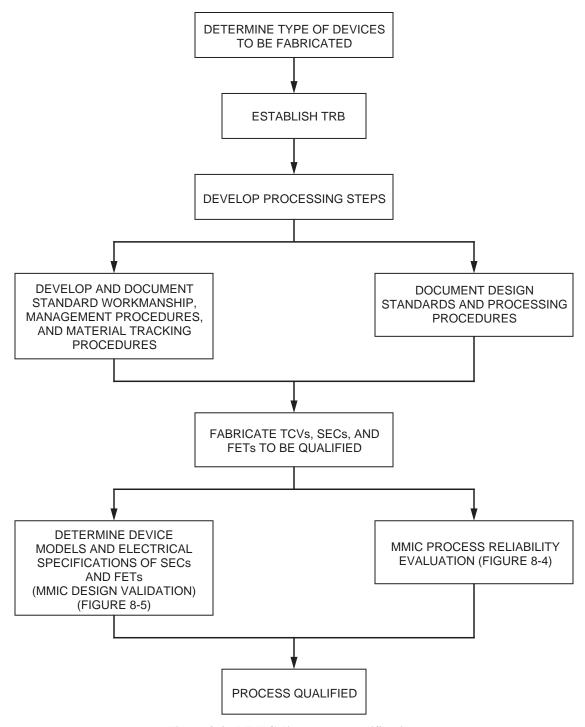

#### III. Process Qualification 146

- A. Process Step Development 149

- B. Wafer Fabrication Documentation 149

- C. Parametric Monitors 149

- D. Design-Rule and Model Development 151

- E. Layout-Rule Development 151

- F. Wafer-Level Tests 151

- G. TCV and SEC Tests 151

- H. Starting Materials Control 152

- I. Electrostatic Discharge Characterization and Sensitivity 152

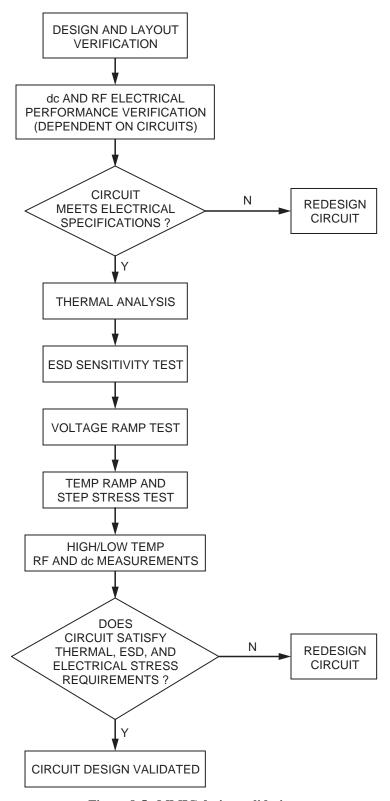

#### IV. Product Qualification 153

- A. MMIC Design, Model, and Layout Verification 153

- B. Thermal Analysis and Characterization 154

- C. Electrostatic Discharge Sensitivity Tests 154

- D. Voltage Ramp 155

- E. Temperature Ramp and Step Stress 155

- F. High/Low Temperature Tests 155

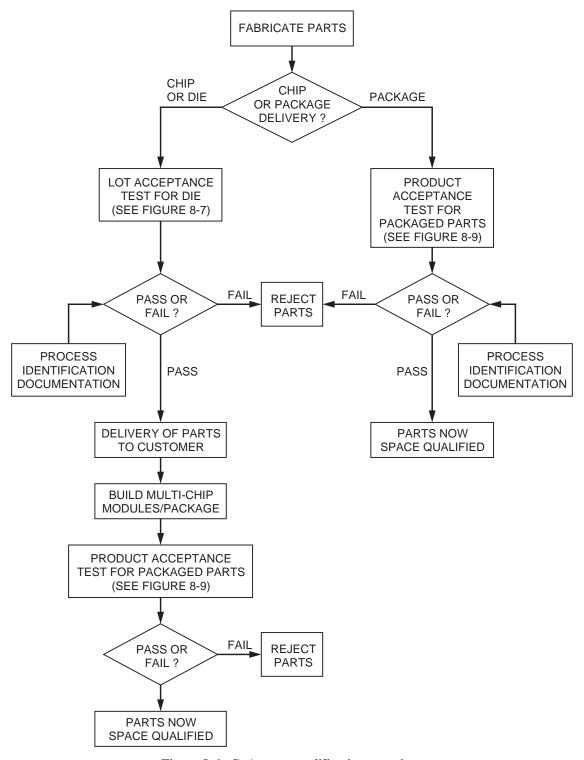

#### V. Product Acceptance 155

- A. Stabilization Bake 156

- B. SEM Analysis 163

- C. Nondestructive Bond Pull Test 163

- D. Visual Inspection 163

- E. IR Scan 164

- F. Temperature Cycling and Shock Screen 164

- G. Mechanical Shock Screen 165

- H. Constant Acceleration 165

- I. Particle Impact Noise Detection 165

- J. Burn-In 165

- K. Leak Test 166

- L. Radiographic 166

References 167

Additional Reading 167

#### Chapter 9. GaAs MMIC Packaging

- I. Introduction 170 (G. E. Ponchak)

- A. Functions of Microwave Packages 172

- B. Types of Microwave Packages 176

Additional Reading 180

II. Die Attachment 181 (G. E. Ponchak)

References 183

III. Flip-Chip Package 184 (R. N. Simons)

References 185

IV. Multichip Module-Dielectric Package 187 (G. E. Ponchak)

References 189

V. Plastic Package 190 (R. N. Simons)

References 192

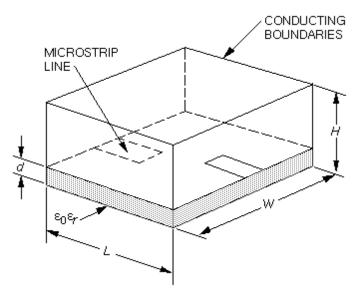

VI. Package Resonance and Field Leakage 194 (R. N. Simons)

References 198

#### Additional Reading 199

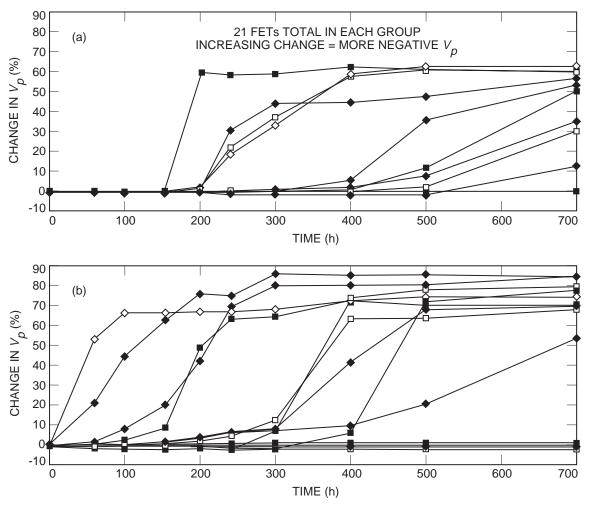

## VII. Hydrogen Poisoning of GaAs MMICs in Hermetic Packages 200 (A. Immorlica and S. Kayali)

References 202

## Chapter 10. Radiation Effects in MMIC Devices 203 (C. Barnes and L. Selva)

- I. Introduction 203

- II. Radiation Environments and Sources 203

- A. The Natural Space Radiation Environment 203

- B. Other Radiation Sources 207

- C. Radiation Shielding 209

- III. Radiation Effects in Semiconductor Devices 210

- A. Ionizing Radiation Effects 210

- B. Displacement Damage Effects 216

- C. Single Event Effects 219

- IV. Radiation Testing 223

- V. Radiation Effects in MMIC Devices and Circuits 227

- A. Ionizing Radiation Effects 227

- B. Displacement Damage Effects 232

- C. Single Event Effects 237

- VI. Conclusions 239

References 240

Acronyms and Symbols 244

#### **Tables**

- 3-1. Room-temperature properties of GaAs 17

- 3-2. Epitaxial layer compositions for basic GaAs-based HEMT and PHEMT devices compared with those of MESFET 41

- 3-3. Comparison of AlGaAs/GaAs HBT and Si bipolar transistors 44

- 3-4. Matrix of solid-state devices and their applications in MMICs 76

- 4-1. Common MMIC failure modes 89

- 4-2. General responsibilities for the failure-mechanism categories 92

- 5-1. Relationship between variations of bias and element values 120

- 7-1. Common parametric monitors 133

- 7-2. Typical test structure information 134

- 7-3. Examples of dc and RF autoprobe test parameters 135

- 8-1. Typical packaged device screening 162

- 9-1. Summary of reliability test conditions and results for fluxless flip-chip thermocompression-bonded bump contacts 185

- 10-1. Total-dose tolerance of various GaAs MMIC devices 228

- 10-2. Ion-bombardment-induced degradation of drain current in GaAs devices 236

- 10-3. Characteristics of four GaAs microwave transistors examined for SEB 238

## **Figures**

- 2-1. Semiconductor cumulative failure distribution 6

- 2-2. Product development cycle 6

- 2-3. Probability of survival to time t, for a constant failure rate 9

- 2-4. Probability of success normalized to the MTBF 10

- 2-5. Semiconductor failure rate 10

- 2-6. Arrhenius plot 12

- 3-1. Unit cube of GaAs crystal lattice 16

- 3-2. Energy band diagram for GaAs 17

- 3-3. Energy band structure of Si and GaAs 18

- 3-4 Drift velocity of electrons in GaAs and Si as a function of the electric field

19

- 3-5. Energy band diagram of GaAs with impurities 22

- 3-6. Schematic and cross section of metal-GaAs junction 25

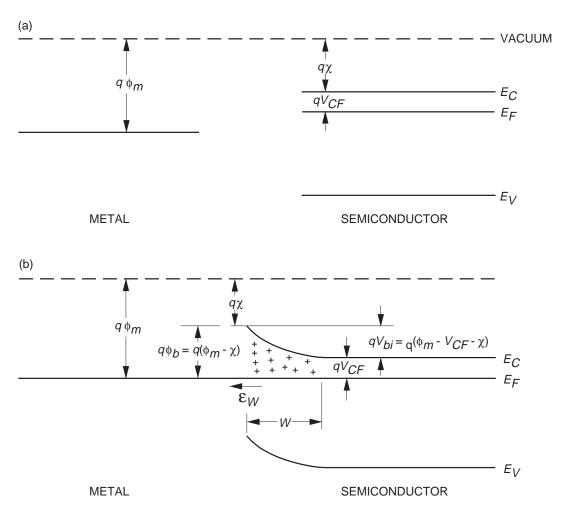

- 3-7. Energy band diagram of metal and semiconductor separate and in contact 25

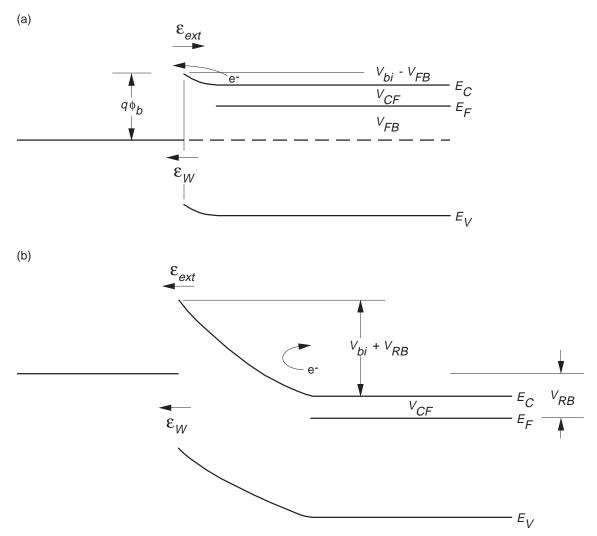

- 3-8. Energy band diagram of metal-semiconductor junction under forward bias and reverse bias 26

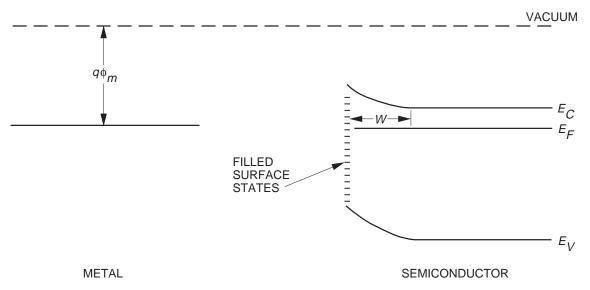

- 3-9. Energy band diagram of metal and semiconductor separate from each other when semiconductor surface states exist 27

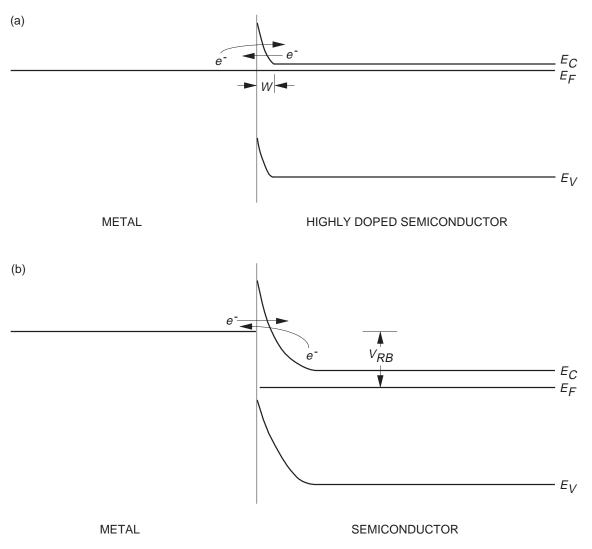

- 3-10. Energy band diagram of metal—n+ semiconductor junction and metal—semiconductor junction under reverse bias 30

- 3-11. GaAs planar diode 31

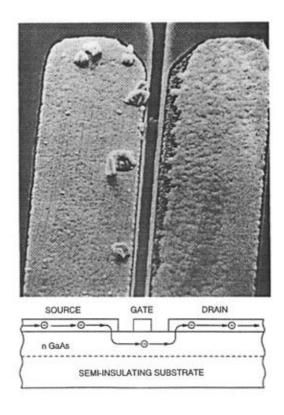

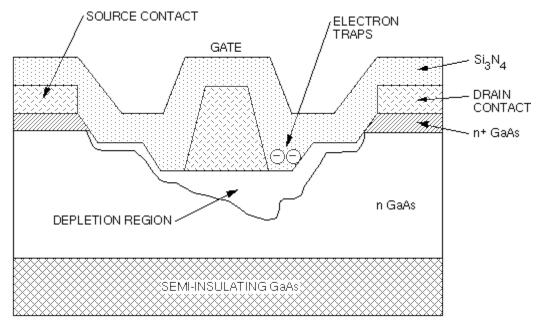

- 3-12. Schematic and cross section of a MESFET 34

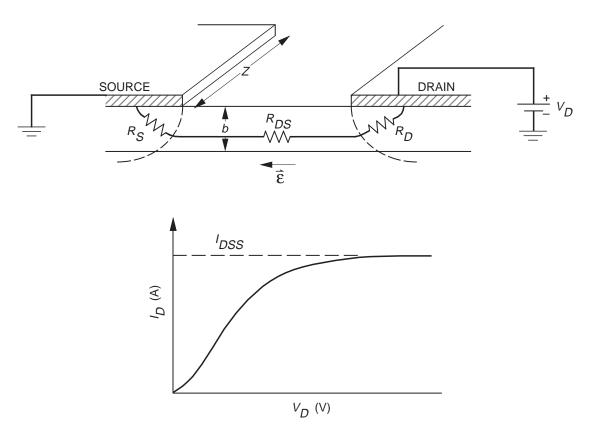

- 3-13 Schematic and I–V characteristics for an ungated MESFET 35

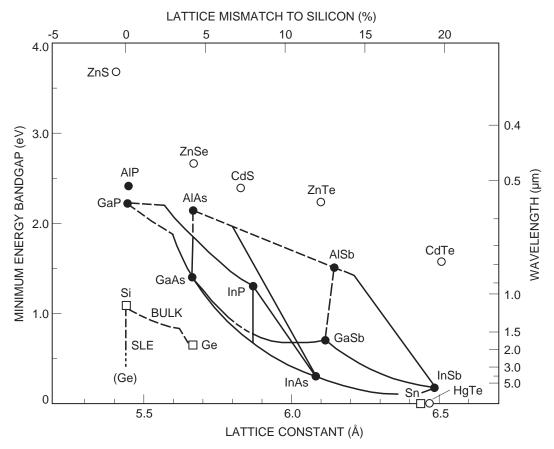

- 3-14. Minimum band-gap energy vs lattice constant data for III–V semiconductors 40

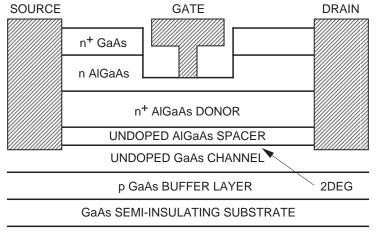

- 3-15. Epitaxial structure of a basic AlGaAs/GaAs HEMT 40

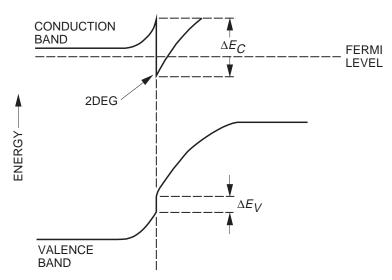

- 3-16. Energy band diagram of a generic AlGaAs–GaAs HEMT showing the 2DEG quantum well channel 41

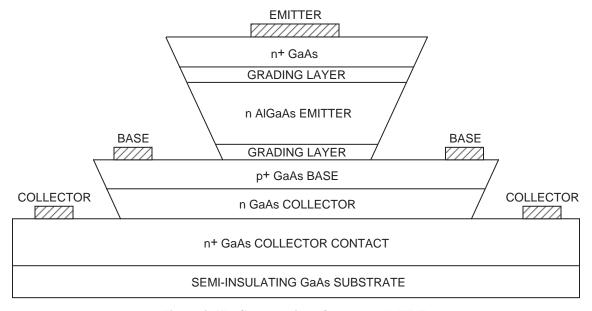

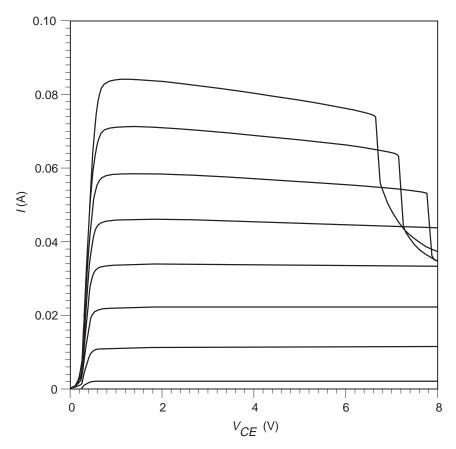

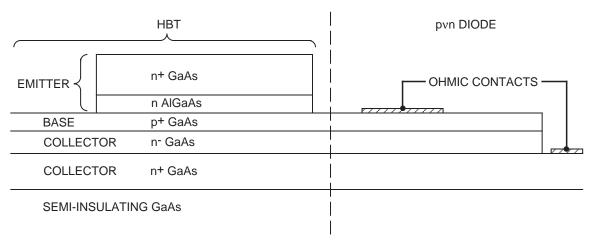

- 3-17. Cross section of an example HBT 45

- 3-18. An HBT cross section showing a thin ledge of AlGaAs 46

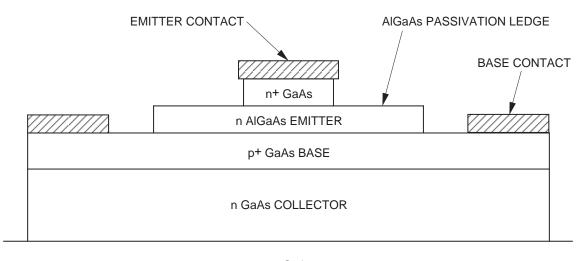

- 3-19. AlGaAs/GaAs HBTs 47

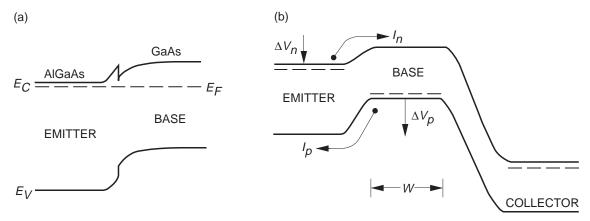

- 3-20. Typical I–V characteristic of a power HBT with multifinger design 49

- 3-21. pnn fabrication from HBT structure 51

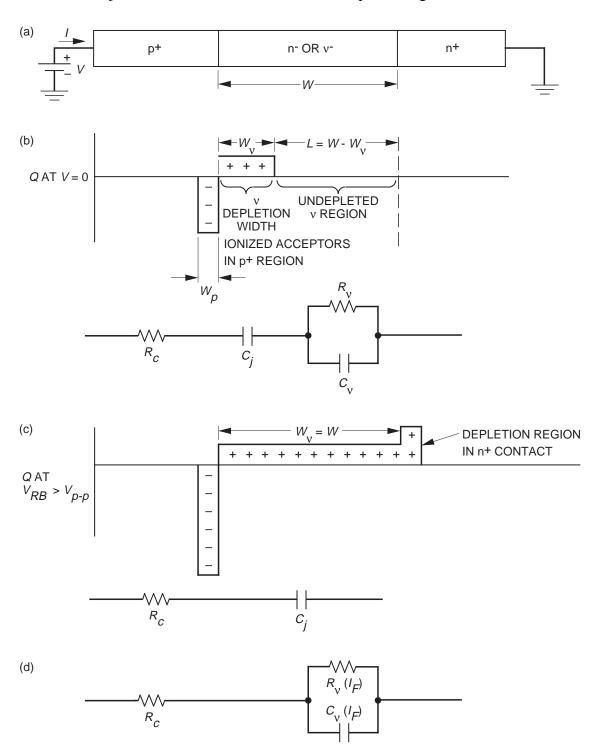

- 3-22. pnn diode 52

- 3-23. Two resistor types in MMIC fabrication 57

- 3-24. MIM capacitor using an air bridge for top-level interconnect 59

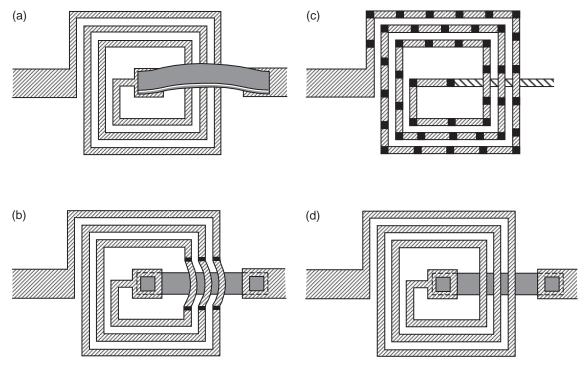

- 3-25. Spiral inductors 60

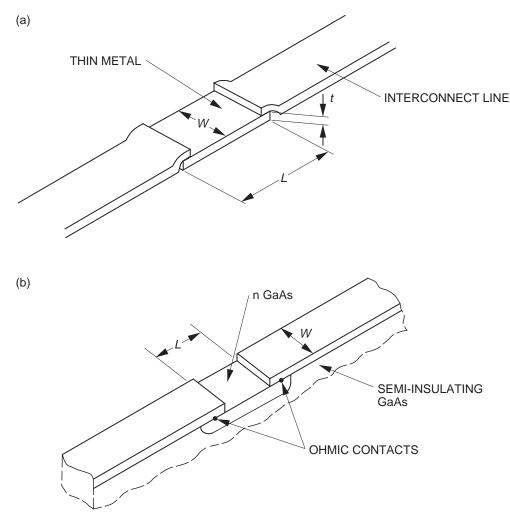

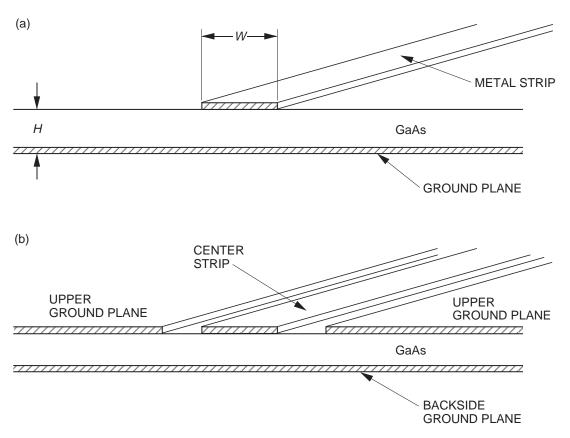

- 3-26. Transmission lines 61

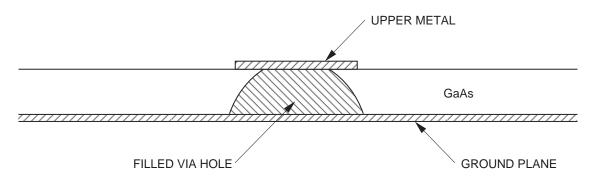

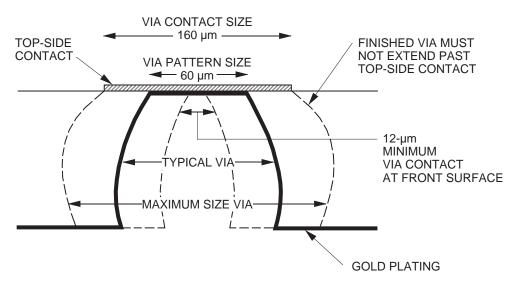

- 3-27. Ideal via hole in GaAs 62

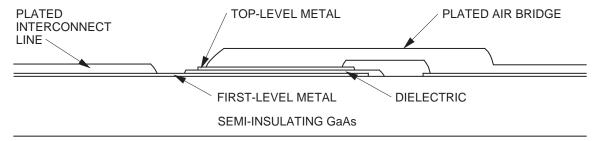

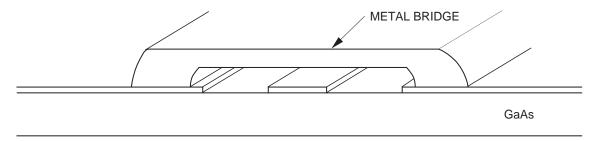

- 3-28. Air bridge connecting coplanar waveguide ground planes 62

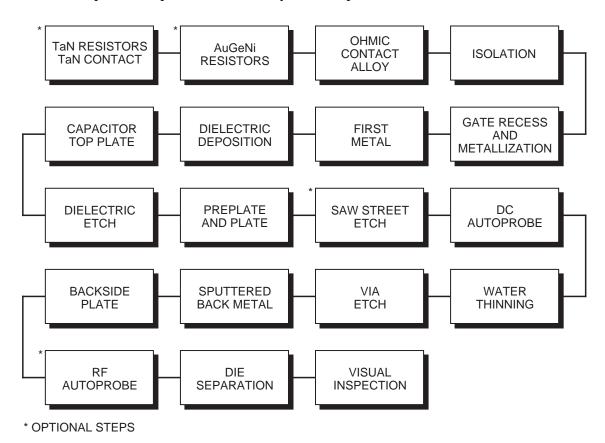

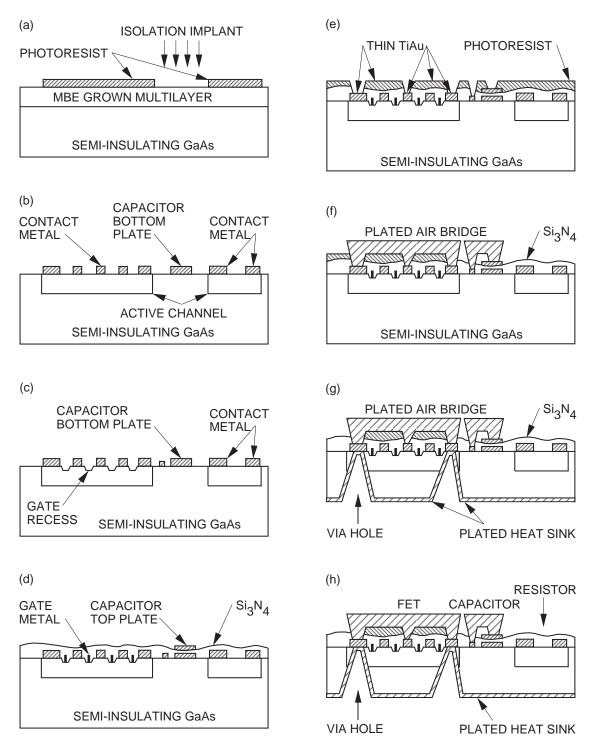

- 3-29. Basic sequence of process steps 64

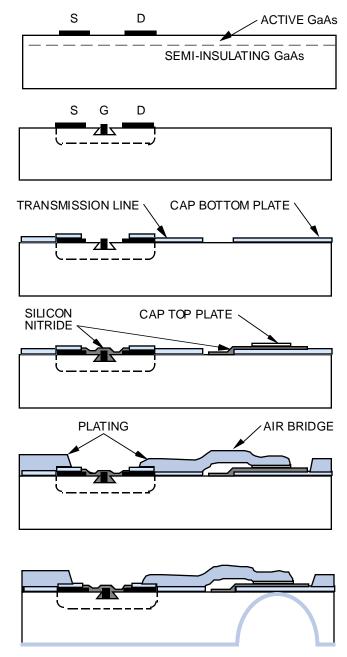

- 3-30. Basic process steps for MESFETs 65

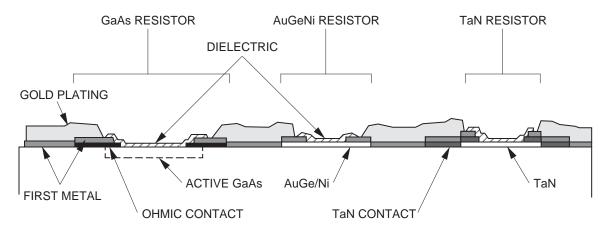

- 3-31. Basic process steps for GaAs, AuGeNi, and TaN resistor 66

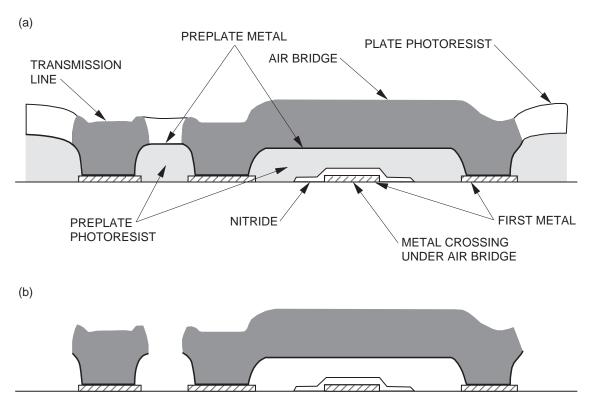

- 3-32. The air-bridge process 67

- 3-33. Via hole with process-variable parameters 67

- 3-34. Typical HEMT/PHEMT process flow 69

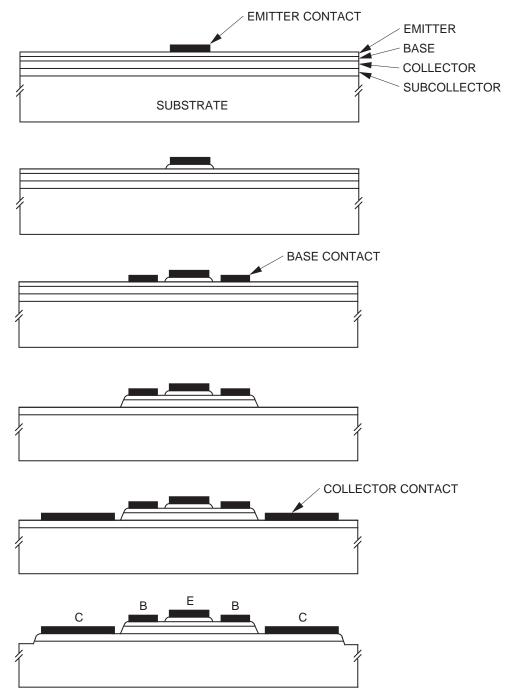

- 3-35. A typical HBT device processing sequence 71

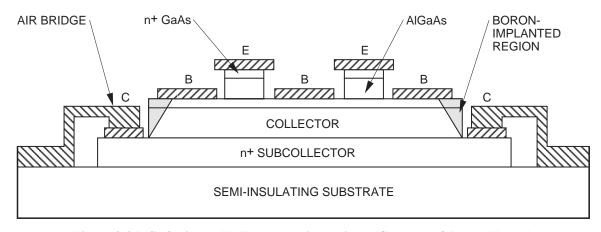

- 3-36. Self-aligned HBT cross-sectional view 73

- 3-37. Schematic cross section of the self-aligned HBT IC structure 73

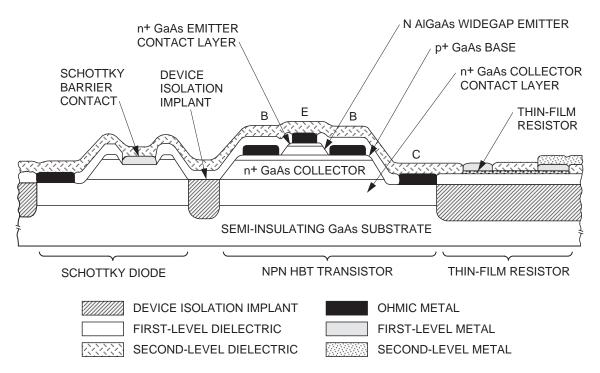

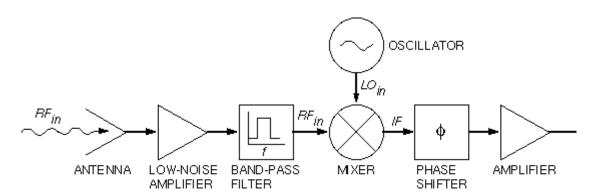

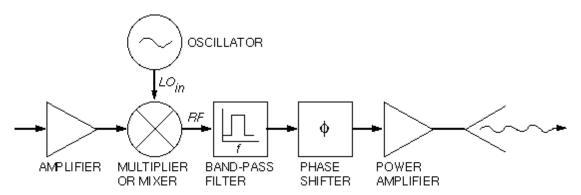

- 3-38. Schematic of microwave receiver 74

- 3-39. Schematic of microwave transmitter 74

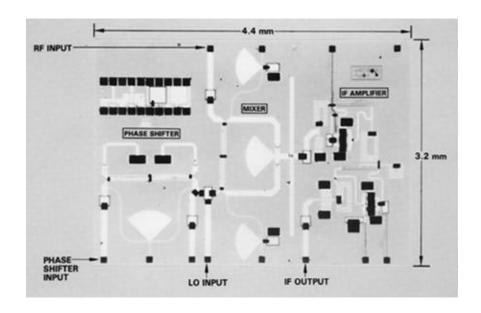

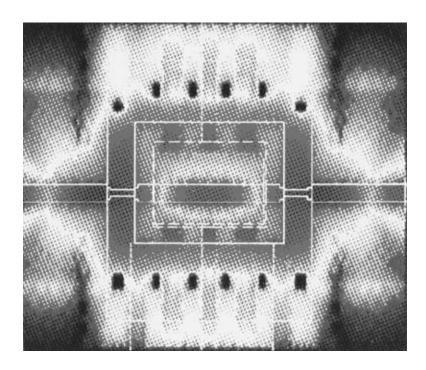

- 3-40. 30-GHz MMIC receiver 75

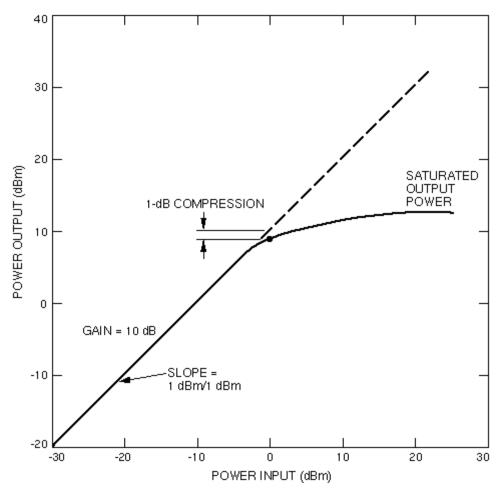

- 3-41. Output power as a function of input power for a typical amplifier 77

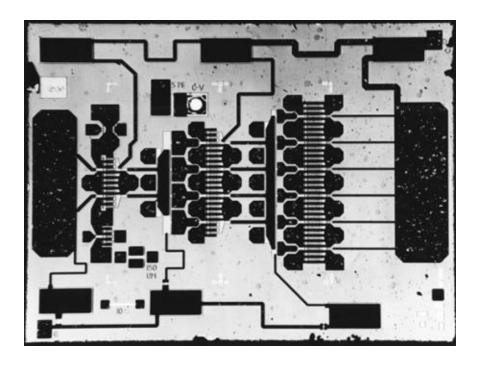

- 3-42. 20-GHz high-power amplifier 79

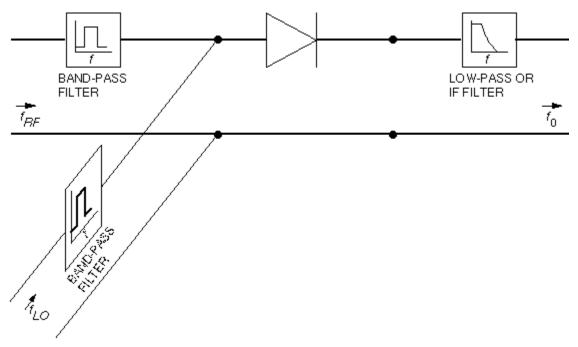

- 3-43. Schematic of simple mixer 81

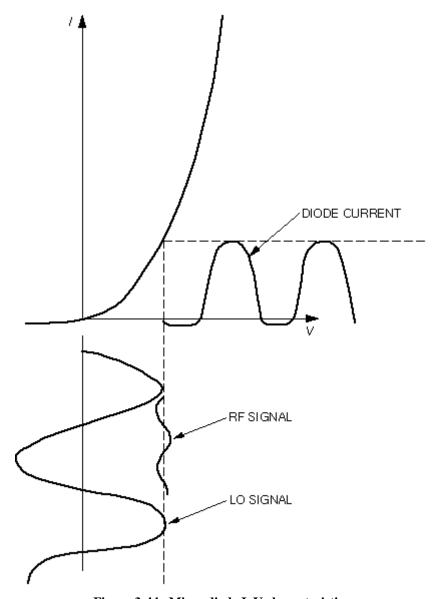

- 3-44. Mixer diode I–V characteristics 82

- 3-45. Schematic of oscillator 83

- 3-46. Power spectrum for a typical oscillator 84

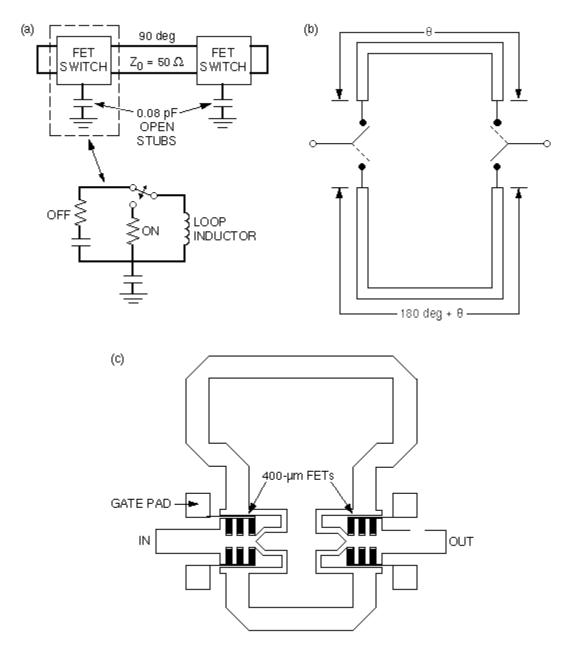

- 3-47. Schematic of reflective-type phase shifter 85

- 3-48. Analog phase shifter comprised of a varactor-tuned reflective load and a Lange coupler 86

- 3-49. Phase shifter comprised of loaded-line and switched-line sections 87

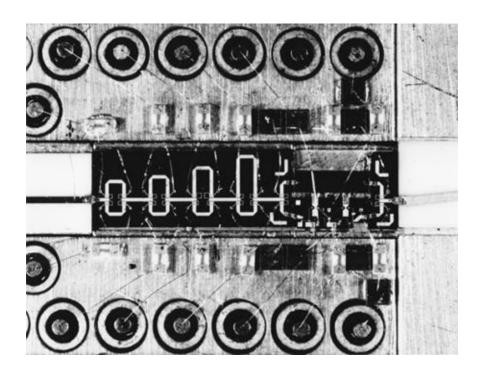

- 3-50. 22.5-deg phase-shifter elements 88

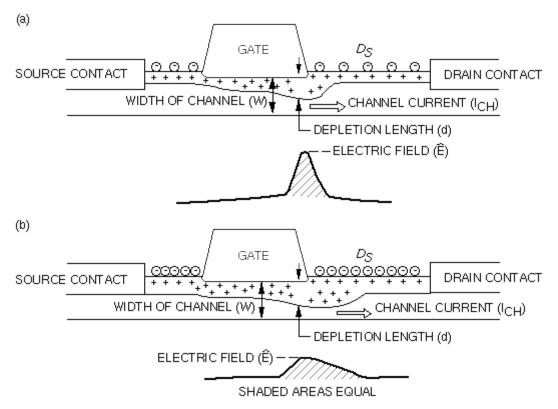

- 4-1. Schematic cross section of a MESFET with different surface charges 94

- 4-2. Metal-atom migration and accumulation 96

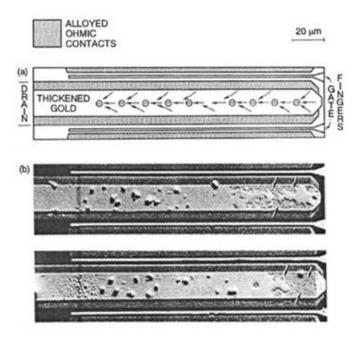

- 4-3. Depletion and accumulation of material in AuGeIn source and drain ohmic contacts 97

- 4-4. Schematic cross section of a degraded MESFET 99

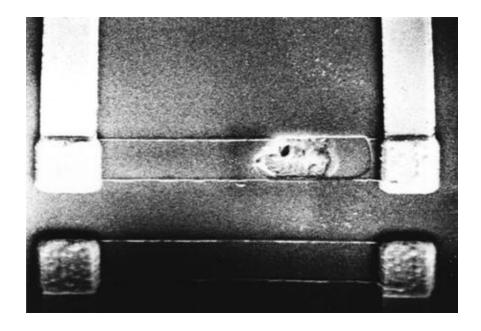

- 4-5. Blown-out gate recess 100

- 4-6. SEM photograph of a failed nickel–chromium resistor 101

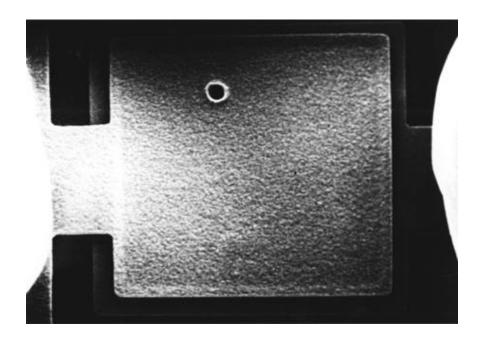

- 4-7. Edge-located ESD failure of a MIM capacitor 102

- 4-8. Interior-located ESD failure of a MIM capacitor 103

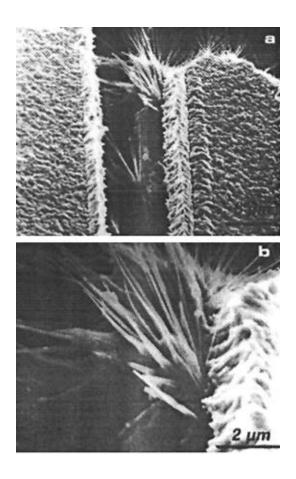

- 4-9. Filamentary growth 104

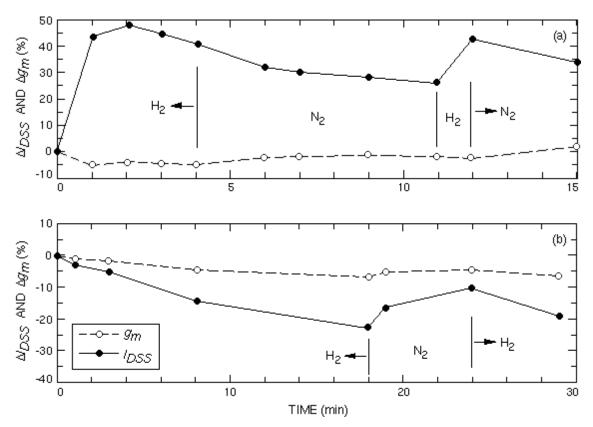

- 4-10. Changes in peak transconductance and drain current at zero gate bias of InP HEMT and GaAs PHEMT 105

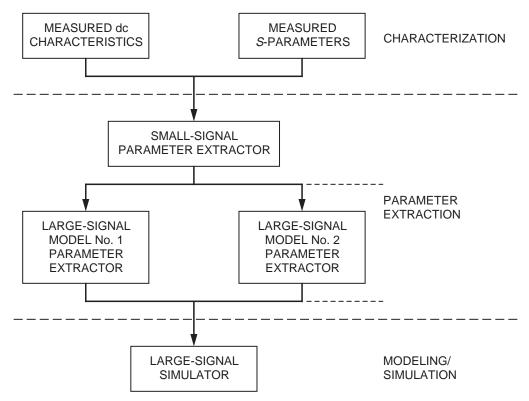

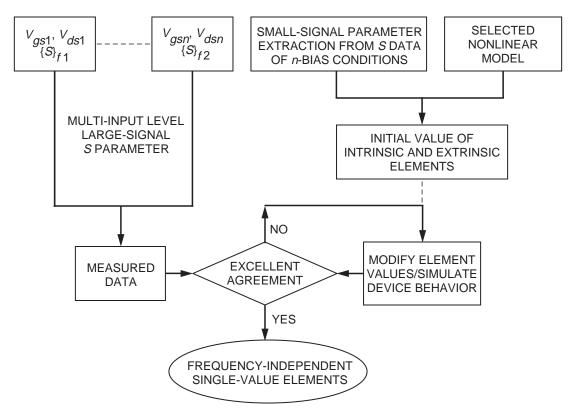

- 5-1. Flow chart of the relationship between characterization, parameter extraction, and modeling 109

- 5-2. Schematic of a MESFET'S material and structure 111

- 5-3. Basic GaAs MESFET's equivalent circuit 111

- 5-4. Flow chart of dc modeling 114

- 5-5. Small-signal direct model extraction process for S-parameter measurement at multiple frequencies 115

- 5-6. Typical flow chart of characterization and parameter extraction for largesignal model 116

- 5-7. Flow chart for MMIC sensitivity analysis 120

- 5-8. Application of the Monte Carlo method to MMIC yield forecasting 121

- 6-1. Typical design flow 129

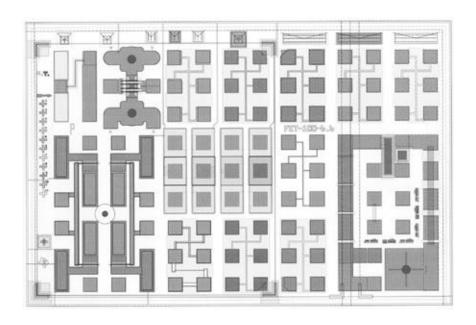

- 7-1. TCV example 132

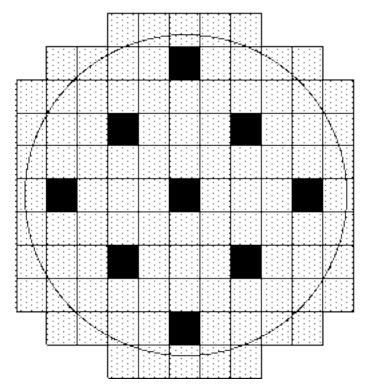

- 7-2. Example of parametric-monitor locations across the wafer 133

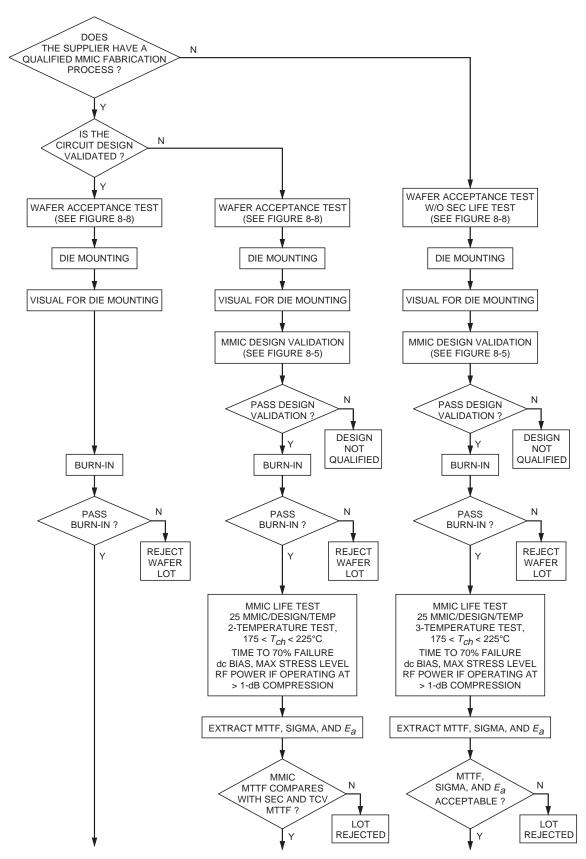

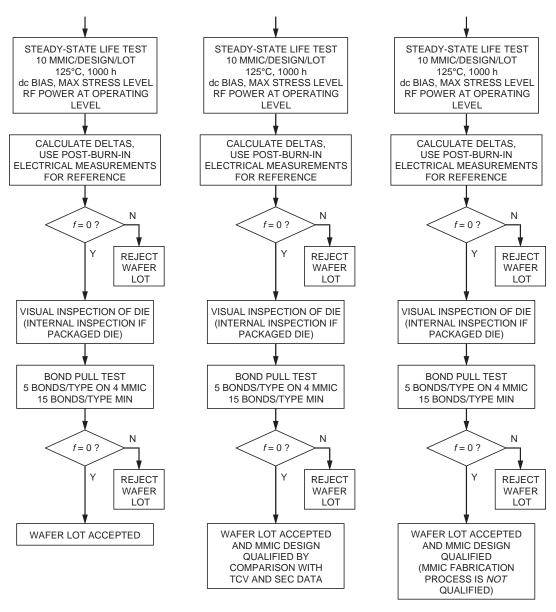

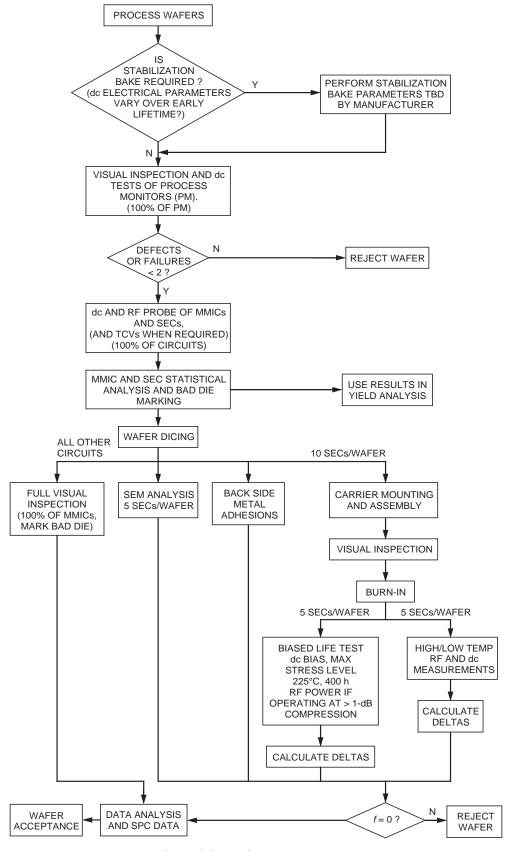

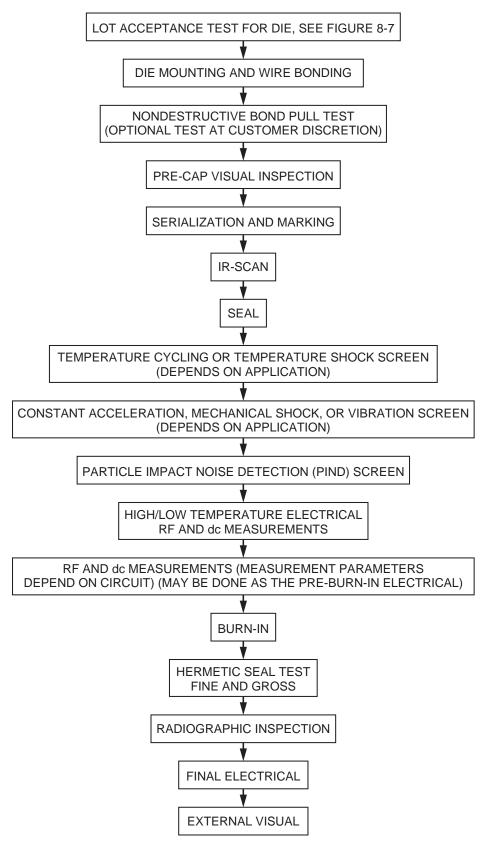

- 8-1. Recommended qualification methodology 138

- 8-2. Reliability audit 140

- 8-3. MMIC die process qualification 147

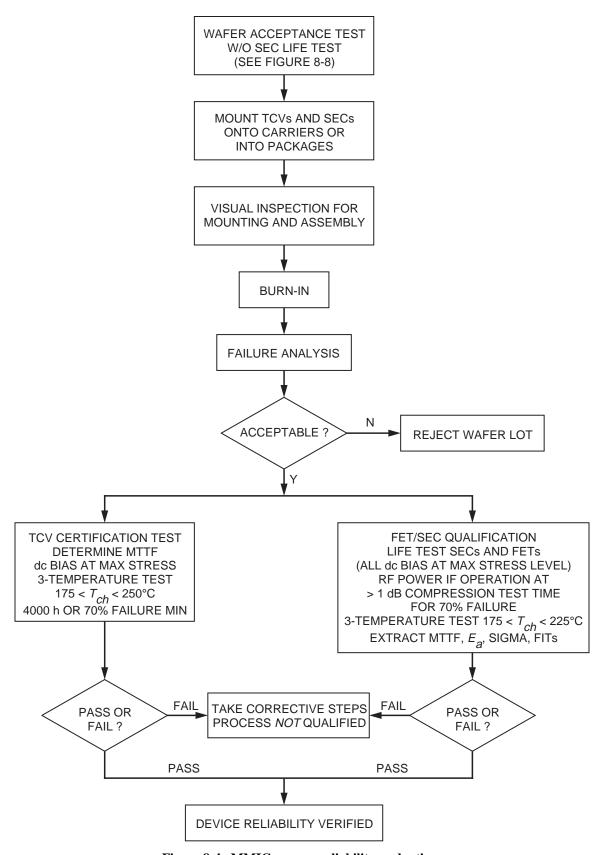

- 8-4. MMIC process reliability evaluation 148

- 8-5. MMIC design validation 150

- 8-6. GaAs part qualification overview 157

- 8-7. Lot acceptance test for die 158

- 8-8. Wafer acceptance test 160

- 8-9. Screening process for packaged MMICs 161

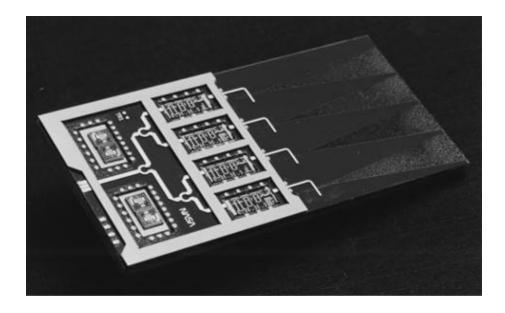

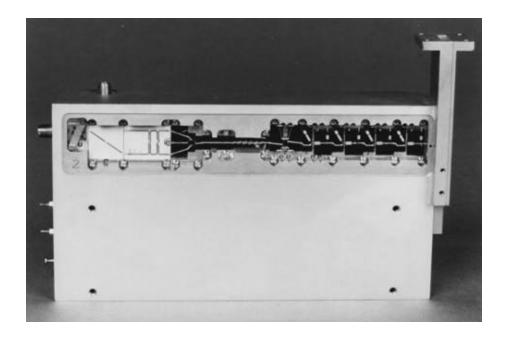

- 9-1. 20- to 40-GHz ceramic MMIC package 171

- 9-2. Prototype of a four-element antenna package 171

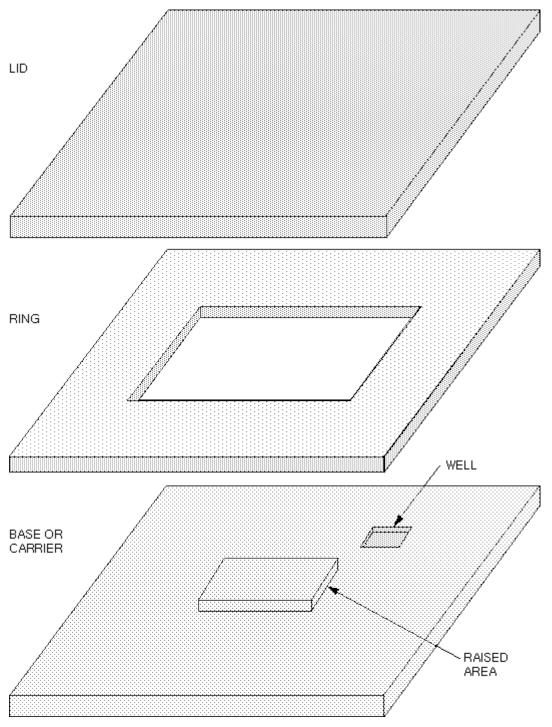

- 9-3. MMIC package 173

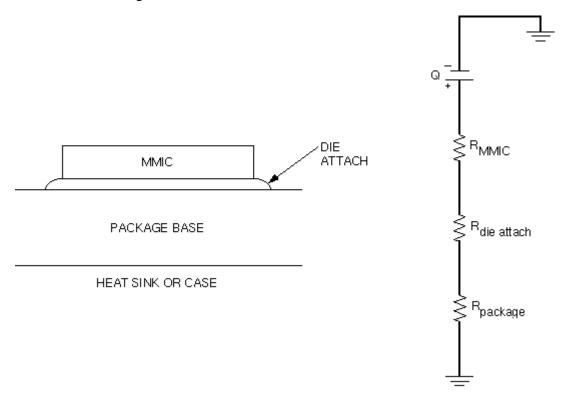

- 9-4. Cross section of MMIC attached to a package and its equivalent thermal circuit 176

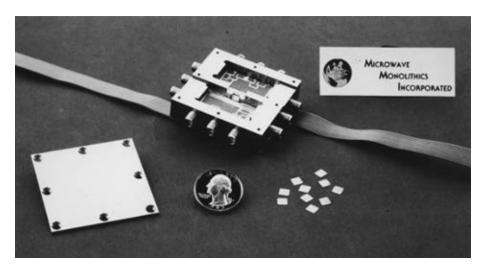

- 9-5. GaAs MMIC switch matrix in a metal package 177

- 9-6. 20-GHz receiver in a metal package 177

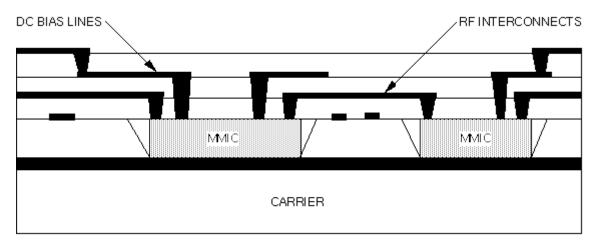

- 9-7. Schematic of thin-film multilayer package with integrated MMICs 180

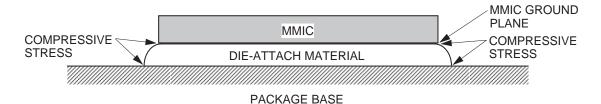

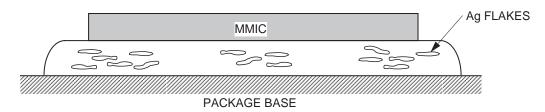

- 9-8. GaAs MMIC in compression 181

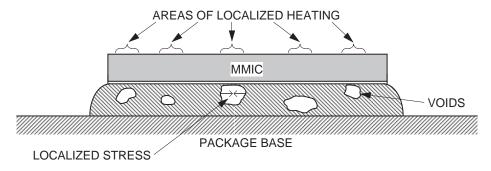

- 9-9. The presence of voids in the die-attach material 182

- 9-10. Bonding material 183

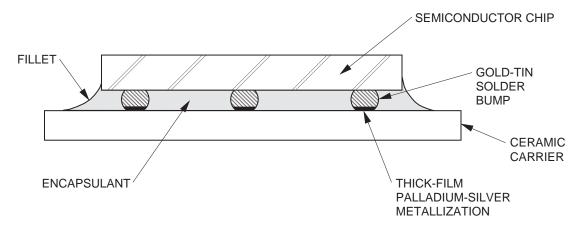

- 9-11. Flip-chip package 184

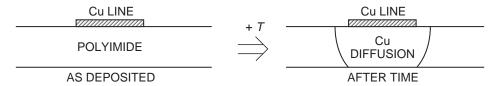

- 9-12. Copper diffusion in polyimide 188

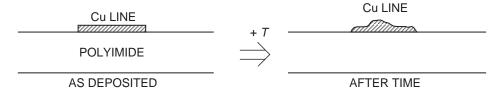

- 9-13. Self-gettering of Cu changes line geometry 188

- 9-14. Stress cracks in polyimide at via holes 188

- 9-15. Typical plastic package showing the onset of a crack 190

- 9-16. Mold compound properties 191

- 9-17. Polyimide die overcoat (PIX) on MMIC die 191

- 9-18. Typical geometry of wire bond with different die settings 192

- 9-19. Multilayer ceramic package with metallized frame walls 194

- 9-20. Ceramic package with metal-filled vias 195

- 9-21. Measured and modeled S-parameters 196

- 9-22. Computed vertical electric-field distribution 197

- 9-23. Partially filled metal cavity with microstrip input/output ports 198

- 9-24. Percent change in pinch-off voltage 201

- 10-1. Schematic diagram of the Earth's Van Allen radiation belts 204

- 10-2. World map contours of electron dose at 500 km 205

- 10-3. Sunspot activity and solar flare events for solar cycles 19, 20, and 21

206

- 10-4. Distribution in energy and abundance of various galactic

- cosmic ray particles 207

- 10-5. Attenuation of galactic cosmic ray Si ions 208

- 10-6. Van Allen belt trapped proton spectra emerging from spherical shields

- of various thicknesses for a 500-km orbit at 60-deg inclination 209

- 10-7. Ionizing-dose failure levels for MOSFET integrated circuits 212

- 10-8. Ionizing-dose failure levels for bipolar integrated circuits 213

- 10-9. Ionizing-dose failure levels for discrete, linear, and digital device families 214

- 10-10. Primary photocurrent magnitudes generated by prompt dose-rate irradiations in various types of diodes 215 10-11. Prompt ionizing dose-rate hardness levels for bipolar and MOS integrated circuit families 216

- 10-12. Prompt ionizing dose-rate hardness levels for discrete device families 217

- 10-13. Neutron hardness levels for discrete devices 219

- 10-14. Neutron hardness levels for integrated circuit families 220

- 10-15. Single event upset in a typical SRAM memory cell 221

- 10-16. Dependence of critical charge for upset on feature size for various integrated circuit technologies 222

- 10-17. SEU rates at geosynchronous orbits for various circuit technologies 224

- 10-18. Change in saturation current of enhancement mode GaAs JFET after irradiation 228

- 10-19. Cross section of GaAs JFET showing transient ionization-induced backgating effect 229

- 10-20. Transient response of drain current to 20-ns electron pulses for GaAs JFETs on two types of substrates 230

- 10-21. Transient drain current response for single- and double-implanted GaAs JFETs 230

- 10-22. Peak-to-peak power upset generated by 50-ns pulses of 40-MeV electrons bombarding TI two-state feedback amplifier MMICs 231

- 10-23. Response of MMIC amplifiers to transient electron pulses 232

- 10-24. Neutron fluence necessary to reduce JFET transconductance by 20% in n-type GaAs and Si 233

- 10-25. Gain degradation of several types of bipolar transistors 234

- 10-26. Effect of neutron irradiation on TI GaAs FET parameters 234

- 10-27. Response of two GaAs MMIC amplifiers to neutron irradiation 235

- 10-28. Single-particle-induced charge collection mechanisms in a GaAs MESFET 237

## **Chapter 1.** Introduction

R. Shaw

This chapter establishes a common reference for the varied backgrounds of the readers. It discusses reliability and quality assurance in general and reviews the effects of new technology on the failure-rate distribution of the product. It also gives the reader an overview of why gallium-arsenide (GaAs) is used and a brief summary of the development of the monolithic microwave integrated circuit.

### I. Why GaAs is Used

Perhaps the primary benefit of GaAs comes from its electron-dynamic properties. In equivalently doped n-type GaAs and silicon, the effective mass of the electric charge carriers in GaAs is far less than that in silicon. This means that the electrons in GaAs are accelerated to higher velocities and therefore transverse the transistor channel in less time. This improvement in electron mobility is the fundamental property that enables higher frequencies of operation and faster switching speeds.

While the principal reason for making transistors out of GaAs is greater speed in performance, which is realized either as a higher maximum frequency of operation or higher logic switching speeds, the physical and chemical properties of GaAs make its use in transistor fabrication difficult. Most of the early development in solid-state electronic devices centered on silicon- and germanium-based materials because of the relative ease with which the material could be processed. Silicon and germanium are elemental semiconductor materials, whereas GaAs is a binary compound. This is the root fact that caused many technical obstacles in the use of GaAs. Other properties not in GaAs' favor for early solid-state device development included a lower thermal conductivity and a higher coefficient of thermal expansion than silicon and germanium. However, as new market applications demanded higher performances that could be achieved only with the superior electron dynamics of GaAs, these obstacles have been overcome.

The markets that drove the breakthroughs in material-growth and devicefabrication techniques of GaAs semiconductors were the defense and space industries. These industries required systems with higher frequency circuits for radars, secure communications, and sensors. Many federal agencies put in place programs to develop GaAs devices as primary products in their systems. The maturity of GaAs led to the emergence of new commercial markets, such as wireless local area networks (WLANs), personal communication systems (PCSs), direct broadcast satellite (DBS) transmission and reception by the consumer, global positioning systems (GPSs), and global cellular communication. These commercial markets required the insertion of GaAs technology to meet system performances not attainable with silicon and germanium. Some of the advances achieved with GaAs technology included the use of higher frequencies to avoid spectrum crowding, new digital transmission techniques that require linear amplifiers at higher RF power levels, and lower voltage/lower current amplifiers to maximize the operating and standby times of equipment that had to be powered by batteries. In some instances, GaAs is the system "enabler," without which there would be no product or service to sell. Although these emerging markets offer advanced services and products to the consumer, several limitations to their acceptance over silicon-based systems exist. One drawback is that the failure mechanisms and reliability of silicon are better understood than those of GaAs. Another drawback is the cost and availability of GaAs

when compared to silicon. The use of silicon in lower frequency analog circuits and in very large scale integration (VLSI) technology has developed proven practices and a strong production base for the semiconductor industry. This manufacturing maturity equates to a lower cost for silicon-based rather than GaAs-based technology. However, when the cost to manufacture is compared to performance, the value added to the system by the GaAs technology in most cases more than pays for the increased fabrication cost. As the WLAN, PCS, DBS, GPS, and cellular markets grow, the cost to manufacture GaAs will decrease, and the issue of using GaAs rather than silicon will hinge on the ability of GaAs to satisfy the technical needs of the marketplace.

### II. Hybrid and Monolithic Integrated Circuits

From 1930 to 1960, microwave or high-frequency technology consisted of circuits manufactured using waveguide: rectangular hollow metal pipes that "guided" the electromagnetic energy to its destination. The design was usually experimental and the production was generally expensive and long. At that time, the microwave engineer was known as a "plumber" and his tool of trade was a hammer. Around 1960, the development of semiconductors in "planar" geometries and the production of cheap, lowloss dielectric materials were the beginnings of the microwave integrated circuit (MIC). This technology was later called hybrid microwave integrated circuitry because the active devices (such as diodes and transistors) and some of the passive elements (resistors, capacitors, and inductors) were discrete components mounted to a dielectric slab or substrate. The MIC utilized metal transmission lines that were photolithographically etched onto the substrate to guide the electromagnetic energy to various components of the circuit. The performance approached the design prediction better than the waveguide predecessor, but many perturbations in the line geometries and inconsistent material properties caused much of the final circuit layout to be experimentally determined. Other factors that made hybrid-circuit production difficult were the labor-intensive processes of assembly and electrical performance testing. The assembly process required mounting each individual discrete device on the substrate, and, because of variations in component placement, the electrical test operation required labor to tune the circuit performance. The attachment of devices to the substrate and the tuning techniques required to make them perform became an art form and a hard process to control. Eventually, at higher and higher frequencies, these processes became the limiting constraints to performance, cost, yield, and reliability.

The idea of a "monolithically" integrated circuit—where the active and passive components are formed on the substrate—eliminated many of the problems with hybrid integrated circuits. The monolithic microwave integrated circuit (MMIC) uses an insulating crystalline material as both the dielectric and the active layer material. For many new applications, GaAs has become the material of choice because of its ability to perform at high frequencies. It also has a high-resistivity semi-insulating property that reduces cross talk between devices. This permits the integration of active (radio-frequency) devices, control (logic) devices, transmission lines, and passive elements on a single substrate.

Unlike the hybrid MICs, a GaAs MMIC's performance cannot be easily "tuned" by adjusting lumped or distributed elements. Once the circuit is processed, its performance is, for the most part, set. Therefore, the design of the MMIC must be based on accurate physical and electrical models for both the passive and active elements, including effects due to manufacturing process tolerances. This design process uses powerful interactive software programs for the synthesis, analysis, and layout of linear

and nonlinear circuits. Development of this software capability has matured since the 1970s, and improvements continue to be made as the technology matures. Many manufacturers have "libraries" of existing device models, which have allowed the MMIC designer to realize the desired performance without having to experimentally characterize the device.

In comparison to the other forms of microwave technology previously discussed, GaAs MMICs offer the following advantages:

- (1) Size and weight reduction.

- (2) Cost reduction for medium- to large-scale production volumes.

- (3) Enhanced system performance from the inclusion of several functions (e.g., RF and logic) on a single circuit.

- (4) Enhanced reproducibility from uniform processing and integration of all parts of the circuit.

- (5) Enhanced reliability from integration and process-control improvements.

- (6) Wider frequency-bandwidth performance from the reduction of parasitics in discrete device packaging.

- (7) Design performance realized without several iterations—the result of processing and material repeatability, and computer-aided design enhancement.

### III. Reliability and Quality Assurance

For any application, the user of the part wants the assurance that the part will continue to function correctly over a given time and under certain environmental conditions. Part failure at any given time takes place when the combined effect of the stresses imposed on the part exceeds the part strength. These statements allude to the time dependency of both part reliability and user expectation. For example, an expendable system might have a useful life of 1 minute while a satellite system must have a predicted life of several years. Each user has a different expectation of part reliability and a different level of commitment to pay for the assurance that the part will meet the expectation. Traditionally, the procurement of highly reliable (hi-rel) parts meant that the user of the component specified to the manufacturer additional requirements to be met in the fabrication of the part. These specifications were usually in terms of recording fabrication process steps, performing additional visual inspections, and incorporating additional screens and burn-in tests. The user of the hi-rel part was expected and usually willing to pay the cost for this increased reliability and quality assurance.

To understand what the user bought with this additional testing requires an investigation of the nature of part failures and their causes or failure mechanisms. It is well documented in the reliability discipline that most products experience a disproportionate number of failures in the early period of their service. This phenomenon, typically referred to as "infant mortality," can arise with any stress applied to the device (e.g., temperature, environmental, and voltage stress). Usually the infant failures occur because of a manufacturing process irregularity that decreased the product's strength in proportion to the strength of the stress imposed. Once this population of infant failures passes, the remaining units have a failure distribution centered around an expected value for a given stress. The long-term failure distribution is

usually determined by the chemical and physical properties associated with the technology, design, material used in the product, and, most importantly, the total strength of the environmental stresses imposed.

As an example, consider the elasticity of a rubber band. As the rubber band is stretched, it will eventually snap. The strength of the force required to snap the band can be recorded. If this process is repeated on several similar rubber bands, there will be a slight variation of the strength required to break each one. This distribution in failure is caused by slight variations in the manufacture of the different rubber bands. The mean value of strength for breakage is determined by the technology, design, material used in the band, and, to a greater degree, the environment (e.g., temperature and humidity) to which the band is exposed. In addition, you would find a few rubber bands that would snap under a very small amount of stress. These unusually weak bands when analyzed would probably show a defect caused in the manufacturing process, such as a thinner band, or a hole in the material, or a slight tear. These defective units are the infant-mortality population. If the fabrication processes are monitored and kept in control, the number of infant failures is reduced.

This bimodal distribution model is applicable to many types of components, including semiconductors, and, with this model, the value of the additional cost associated with a hi-rel part specification can be understood. Traditionally, a user procuring a hi-rel part would specify that the manufacturer perform stress tests to delete the infant-failure population from the delivered units. In addition, the user of the hi-rel part would specify that the manufacturer control the fabrication processes to reduce the total size of the infant-mortality population. With regard to the mean-failure, the hi-rel user usually specified that the manufacturer calculate a predicted mean-time failure-rate figure of merit. Generally, with a mature technology and manufacturing process such as that used with silicon, this calculation was a meaningful estimate based on the complexity of the circuit and the normal environmental conditions imposed on the circuit during operation. This traditional method of hi-rel procurement using individual part specifications was effective in achieving a part that was more reliable than a commercial product. The additional cost incurred to achieve this level of reliability and quality assurance was considered justified and required to achieve a confidence that a system failure would not occur during the mission.

However, today the large commercial markets of WLAN, PCS, DBS, GPS, and cellular telephony demand the quality and reliability of the hi-rel user but at consumer prices. These high-volume markets have impacted the business philosophy of the semiconductor manufacturer. Many of the manufacturers now fabricate their standard commercial product line utilizing statistical process control for repeatability and uniformity. This has greatly reduced the infant-mortality population without having to impose the hi-rel part specification. Hi-rel users can take advantage of this industry change to decrease the cost of part procurement without adversely affecting the reliability and quality assurance of system performance.

Inasmuch as semiconductor manufacturers have reduced the infant mortality population by improving repeatability in fabricating the devices, the long-term failure mechanisms of GaAs cannot be assumed to be predictable based on silicon technology. The hi-rel user must understand that many of the failure mechanisms associated with silicon devices do not apply to GaAs MMICs, and new device structures bring new failure mechanisms. Many of the traditional assumptions for mean-time failure rate predictions do not hold for these new devices. Thus, today's hi-rel user must be more aware of measurement-based predictions of long-term failure rate over calculation-based predictions. This usually impacts the procurement of the hi-rel part by including a

measurement demonstrating the long-term reliability of the technology to be used. Typically this can be done by some method of accelerated-life test.

This guidebook proposes a hi-rel qualification methodology that does not utilize the product specification philosophy. Rather, the philosophy proposed envisions a methodology that includes a process qualification and a product qualification. The process qualification involves the verification of statistical process control to insure consistent fabrication from device to device. The process qualification works with the manufacturer's knowledge of how to produce a reliable part within the standard processes of the production line. This enables a lower cost and a shorter delivery time. The product qualification is a validation of the circuit to perform to a minimum performance under stress and environmental conditions. It usually includes a measurement demonstrating the failure rate of the part. With this two-part qualification plan, the technology, the fabrication, and the part are verified to meet the expected level of quality and reliability.

#### **Additional Reading**

Deyhimy, I., "Gallium Arsenide Joins the Giants," IEEE Spectrum, Vol. 32, No. 2, pp. 33–40, February 1995.

*High-Power GaAs FET Amplifiers*, J. L. B. Walker, Editor, Artech House, Inc., Norwood, MA, 1993.

Jensen, F., and Niels E., Burn-In, An Engineering Approach to the Design and Analysis of Burn-In Procedures, John Wiley & Sons, New York.

## Chapter 2. Reliability Overview

R. Shaw

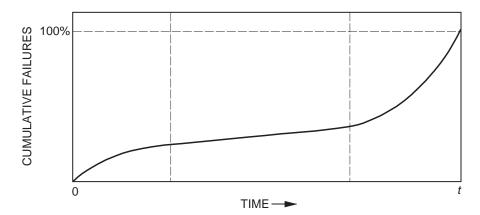

Reliability has been defined as the probability that an item will perform a required function under stated conditions for a stated period of time. Hence, reliability can be modeled as a probability distribution. For most semiconductor devices, a cumulative failure distribution between 0% and 100%, as shown in Figure 2-1, will be representative of its behavior over a period of time, *t*.

Figure 2-1. Semiconductor cumulative failure distribution.

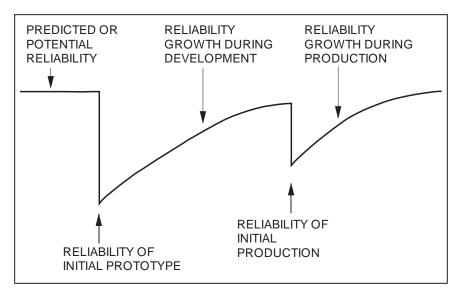

Factors influencing the reliability of a product cover a large range of variables, including design, manufacturing, the eventual application, and the human involvement factor at each stage of production. In fact, history has shown many times that the reliability of a product from development to production follows the graph of Figure 2-2. Here the predicted or potential reliability of the product has been calculated or compared to the demonstrated reliability of a similar product. What causes the low reliability of the

Figure 2-2. Product development cycle.

initial prototype could be a flaw in design, an unknown manufacturing process problem, the cumulative effect of several environmental stresses on the part, or a combination of several of these factors. Once the initial prototype has been produced, the reliability of the part improves as development progresses and failure mechanisms are determined and overcome. With transition of the product to a manufacturing production line, reliability usually regresses. This reduction in reliability could be caused by the change from a development or research fabrication process to a production line fabrication process. The manufacturing production line environment can be very different from the environment of the research and development pilot line. Also, at this point in the product's life cycle, the human-involvement factor is usually at its most drastic transition, causing many variances in the fabrication process.

These reliability shortcomings from design to production can be minimized by incorporating, as early in the development cycle as possible, statistical process control methodologies in the fabrication of the part and by performing life-test measurements. Implementing these techniques forces reliability growth to occur in conjunction with product development. For the manufacturer, this means a quicker time-to-market cycle of a reliable product that will not require costly warranty repair or replacement. For the user, it means that the state-of-the-art product can be confidently incorporated in his advanced system.

#### I. Failure

The definition of a failure is important to any analysis on semiconductor device reliability. A failure could be classified into two groups:

- (1) Degradation failures, where an important parameter of a component drifts so far from its original value that the component no longer functions properly.

- (2) Catastrophic failures—the end of component life; i.e., complete destruction of the component.

Part failure at any given point in time takes place when the combined effect of the stresses imposed on the part exceeds the part strength. Typical factors that influence the failure rate of semiconductors are; temperature, voltage level and polarity, complexity, base material, handling and electrostatic discharge, and humidity.

#### A. Physical Failure Mechanisms

Although both passive and active components of GaAs MMICs are subject to reliability problems, the active elements (such as a FET) are often the limiting factor. Ohmic contacts on FETs can be a reliability limiting factor, gradually degrading in contact resistance as diffusion acts to destroy the ohmic alloy, but the major limitations have been found to be related to the FET channel. The exact nature of these channel defects may vary, but the effects are consistent with a reduced channel thickness, as though the gate were "sinking" into the material.

Another major failure mechanism in semiconductors, both silicon and GaAs, is metal migration. Metal migration is the physical movement of metal in a conductor caused by current flow. Electron scattering from metallic atoms literally pushes these

atoms in the direction of electron flow. Metal can be depleted from one part of the conductor and accumulate at a nearby part. At the depletion site, the cross-sectional area of the conductor is reduced. This increases the current density, which increases the effect even more and can lead to burnout at the thin portion of the conductor. In addition, a buildup of metallization at accumulation points can lead to shorts in metal above the buildup, such as air bridges or capacitor plates. Electromigration is the main reason the current density in metallic elements on MMICs is limited to approximately  $2 \times 10^5 \, \text{A/cm}^2$ . The "fusing" (burnout) current density is much greater.

Although the above discussion centered on FET channel failures and electromigration as major failure mechanisms in GaAs MMICs, lack of careful attention to other elements can result in severe reliability problems. Accelerated-life testing is needed to identify and remove such limitations. With these precautions, the median lifetimes of GaAs MMICs can exceed  $1 \times 10^6$  h at normal operating temperatures.

Chapter 4, "Basic Failure Modes and Mechanisms," provides further information and discussion on this topic.

#### B. Radiation Failure Mechanisms

The ability of GaAs devices to withstand radiation is important in both space and military applications. Objects in Earth orbit are subjected to radiation from the radiation belts surrounding the planet. The cumulative dose absorbed over time can be considerable, and, of course, shielding in space applications must be minimal for the obvious weight and cost considerations. Many military applications require the ability to withstand intense radiation caused by nuclear explosions. The amount of radiation generated over a short period by nuclear events can be very high. In summary, there is interest in the ability of GaAs devices to withstand both long-term cumulative radiation and high dose rates over short periods. GaAs devices generally have greater radiation tolerance than do silicon devices, and this is one of their advantages in radiation environments.

Chapter 10, "Radiation Effects in MMIC Devices," provides further information and discussion on this topic.

## II. Quantifying Reliability

Quantifying reliability is achieved from the concept of reliability as a probability distribution. The probability of a component surviving to a time t is the reliability, R(t), of the component, and is expressed as

$$R(t) = \frac{\text{number surviving at instant } t}{\text{number at time } t = 0}$$

The failure rate can be expressed as f(t), where

$$f(t) = \frac{\text{number failing per unit time at instant } t}{\text{number surviving at instant } t}$$

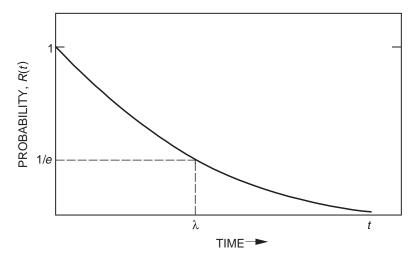

The failure rate can therefore be defined as the probability of failure in unit time of a component that is still working satisfactorily. For constant failure rate f, R(t) is given by

$$R(t) = \exp(-ft)$$

R(t) is therefore an exponentially varying function of time, as shown in Figure 2-3.

Figure 2-3. Probability of survival to time t, for a constant failure rate.

The failure rate, f(t), is given as the number of units failing per unit time. In practice, the number of components failing per second is a fraction of a percent; to obtain more manageable values the units are scaled. Therefore, f(t) may be expressed as the percent (%) failure per  $1 \times 10^6$  h or as the number of devices failing in  $1 \times 10^9$  h. The latter unit is known as the FIT and is commonly used as the unit of reliability:

1 FIT = 1 failure/1

$$\times$$

10<sup>9</sup> device h

The mean number of failures in a given time is defined by the mean time between failures (MTBF) and is another commonly used method of quantifying component reliability. Assuming the failures occur randomly at a constant failure rate, the MTBF is given by

$$MTBF = 1/f$$

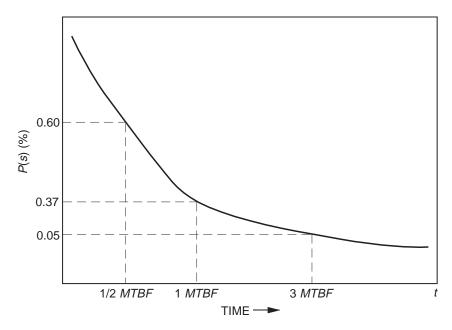

This may also be written as the probability of success or zero failures:

$$P(s) = e^{(-t/MTBF)}$$

where

$$P(s)$$

= probability of success  $t$  = time

Figure 2-4 shows P(s) versus time as normalized to MTBF. From this plot it can be seen that after 1/2 MTBF, the probability that there will be no failures is 60% and 37% after 1 MTBF.

Figure 2-4. Probability of success normalized to the MTBF.

When modeling failures, confidence limits are put on the distributions indicating the extent to which the data are representative of a batch of components. For example, a large sample (>  $1 \times 10^5$  devices) resulting in  $1 \times 10^3$  failures in  $1 \times 10^{12}$  device hours would indicate a failure rate (f) of 1 FIT. This value of f would have a much higher confidence limit than that of one device operated continuously for  $1 \times 10^9$  h, after which time it fails.

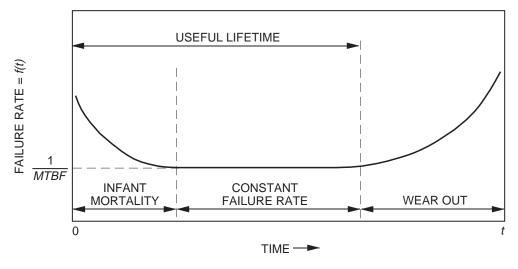

A common graphical interpretation of the failure rate is shown in Figure 2-5. This model is known as the "bathtub" curve and was initially developed to model the failure rates of mechanical equipment. However, it has now been adopted by the semiconductor industry and has become an integral part of semiconductor reliability theory.

Figure 2-5. Semiconductor failure rate.

The bathtub curve in its simplest form consists of the three regions shown in Figure 2-5. The failure rate is theorized to be high at the start, dropping off as the weaker devices fail early. The failure rate then approaches a constant as the components enter their useful lifetime. Failures in this period can be attributed to random overload of the components. Finally, wear-out occurs and the curve increases sharply.

### **III.** GaAs Device Reliability

GaAs device reliability involves probability statistics, time, and a definition of failure. Given a failure criterion, the most direct way to determine reliability is to submit a large number of samples to actual use conditions and monitor their performance against the failure criteria over time. Since most applications require device lifetimes of many years, this approach is not practical. To acquire MMIC reliability data in a reasonable amount of time, most people have used accelerated-life tests at high temperatures. By exposing the devices to elevated temperatures, it is possible to reduce the time to failure of a component, thereby enabling data to be obtained in a shorter time than would otherwise be required. Such a technique is known as "accelerated testing" and is widely used throughout the semiconductor industry. The rate at which many chemical processes take place is governed by the Arrhenius equation:

$$r = A \exp\left(\frac{-E_a}{kT}\right)$$

where

r =rate of the process

A = a proportional multiplier, which can be a function of temperature (A = A(t))

$E_a$  = a constant known as the activation energy for a given process

$k = \text{Boltzman'} \text{ s constant}, 8.6 \times 10^{-5} \text{ (eV / K)}$

This equation has been adopted by the semiconductor industry as a guideline by which the operation of devices in varying temperature conditions can be monitored. Experimental data obtained from life tests at elevated temperatures are processed via the Arrhenius equation to obtain a model of device behavior at normal operating temperatures. Rearranging the Arrhenius equation allows the temperature dependence of component failure to be modeled as follows:

$$\ln \frac{t_2}{t_1} = \frac{E_a}{k} \left( \frac{1}{T_2} - \frac{1}{T_1} \right)$$

where

$t_{1,2}$  = time to failure

$E_a$  = activation energy in electron volts (eV)

T = absolute temperature in K

To properly analyze life-test data requires the adoption of a mathematical failure distribution. Several are commonly used, including the normal, lognormal, exponential, and Weilbull distributions. Most of the test operators have adopted the lognormal

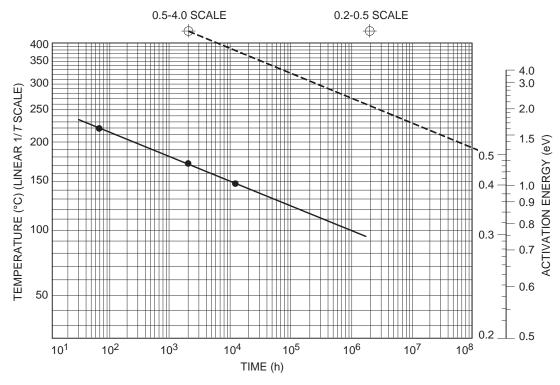

distribution because it most closely fits the measured reliability data from life-tested GaAs semiconductor devices. The lognormal graph is a plot of normal cumulative-percent-failure versus log time. If the life-test data fit a straight line on this graph, the data fit the lognormal distribution. The intersection of this line with 50% cumulative failure indicates the median lifetime. Median life is the time it takes for half of the devices to fail. Figure 2-6 shows a typical Arrhenius plot.

To accurately predict lifetimes at normal operation temperatures, at least three different high-temperature life tests must be performed. The median life from each of the three tests is transferred to an Arrhenius plot and fit with a line. The slope of the line is the activation energy. Median life at any temperature can then be determined. Median life should not be confused with mean time to failure (MTTF). *MTTF* is the reciprocal of the instantaneous failure rate. *MTTF* is not constant with time due to the lognormal failure distribution. One must specify an operation time to calculate the exact *MTTF*. However, a close approximation to the average *MTTF* is calculated as follows:

$$MTTF = T_{op} * \exp(sigma^2 / 2)$$

where

$T_{op}$  = median life at the desired operating temperature sigma = the lognormal standard deviation

Figure 2-6. Arrhenius plot. (Courtesy of Artech House.)

Ideally, accelerated life tests should be conducted with very large sample sizes. However, this is not always practical or economical. The sample size determines the confidence in the lifetime predictions. The smaller the sample size, the less confidence

we have in the prediction. Confidence limits are defined in terms of percentage. For example, an upper and lower 90% confidence limit would indicate that repeating the life test 10 times, 9 out of 10 tests would predict a median life between the two limits. Confidence limits can be calculated for median life with the following equation:

upper limit =

$$T_{test}$$

\* exp  $\left[\left(t(df, alpha) * sigma / N\right)\right]$

lower limit =  $T_{test}$  \* exp  $\left[\left(-t(df, alpha) * sigma / N\right)\right]$

where

$$T_{test}$$

= median life at test temperature  $t(df, alpha)$  = value from students'  $t$  distribution  $df$  = degrees of freedom  $(N-1)$   $alpha$  =  $(1\% \text{ confidence})/2$   $N$  = sample size

It is apparent that knowledge of temperature is fundamental in obtaining accurate reliability data from accelerated temperature testing. A GaAs device or MMIC with active elements will generally have areas, such as FETs, that are far hotter than other areas. Thin-film resistors can also be significantly hotter than surrounding portions of the chip. The chemical or physical changes that lead to failure usually occur in these hotter regions. Therefore, one needs to know the temperature of these regions to obtain accurate determinations of activation energy. Of course, *MTTF* can be determined as a function of any convenient temperature, such as the base-plate temperature. However, even in this case, comparison data from differing institutions are facilitated if the temperature at the failure site, such as the FET, is used.

GaAs is a relatively poor thermal conductor; thermal conductivity of GaAs is less than one-third that of Si at room temperature. Further, the active parts of GaAs devices, such as the gate channel regions of FETs, are also very small. These two factors mean that active areas on GaAs devices can be appreciably hotter than nearby regions of the device, and significantly hotter than the ambient or base-plate temperature. The thermal conductivity of GaAs decreases with increasing temperature. This means that as the ambient or base-plate temperature increases, the temperature differences within the chip also increase. The buildup of heat at active devices is characterized by the thermal resistance of the device. The thermal resistance is defined as the temperature difference between the hottest spot and some reference spot, usually the ambient or base-plate temperature, divided by the power dissipated in the device. Therefore, thermal resistance is expressed in °C/W. Note that thermal resistance will normally vary with device size and will certainly vary as the thickness of the die.

Since most GaAs device failures occur in the FET channel, all life-test data are referenced to the channel temperature. The importance of accurately determining the channel temperature of each device submitted to life test cannot be overstressed. Variables affecting the channel temperature include ambient temperature, device thermal impedance, package and mounting materials, power dissipation, and RF levels. Extensive reliability life tests on numerous GaAs components have been performed since the early 1980s. Typical measured activation energies range from 1.2 eV to 1.9 eV.

## **Additional Reading**

*High-Power GaAs FET Amplifiers*, J. L. B. Walker, Editor, Artech House, Inc., Norwood, MA, 1993.

Jensen, F., and Niels E., Burn-In, An Engineering Approach to the Design and Analysis of Burn-In Procedures, John Wiley & Sons, New York.

Amerasekera, E. A., *Failure Mechanisms in Semiconductor Devices*, John Wiley & Sons, New York, 1987.

# Chapter 3. GaAs Properties, Device Structures, and Circuits

L. Aucoin, Y. C. Chou, A. N. Downey, R. Ferro, S. Kayali, G. E. Ponchak, and R. R. Romanofsky

## I. GaAs Material Properties

#### S. Kayali

GaAs is a III–V compound semiconductor composed of the element gallium (Ga) from column III and the element arsenic (As) from column V of the periodic table of the elements. GaAs was first created by Goldschmidt and reported in 1929, but the first reported electronic properties of III–V compounds as semiconductors did not appear until 1952 [1].

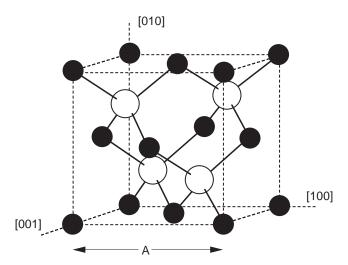

The GaAs crystal is composed of two sublattices, each face centered cubic (fcc) and offset with respect to each other by half the diagonal of the fcc cube. This crystal configuration is known as cubic sphalerite or zinc blende. Figure 3-1 shows a unit cube for GaAs and Table 3-1 provides a listing of some of the general material characteristics and properties.

Figure 3-1. Unit cube of GaAs crystal lattice.

#### A. Energy Band Structure

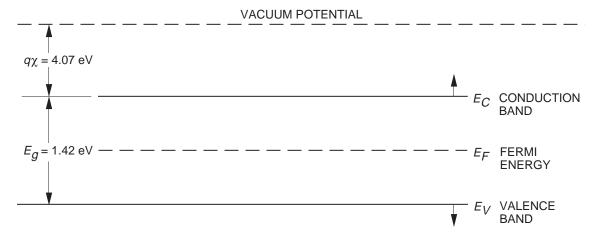

As a result of the laws of quantum mechanics, electrons in isolated atoms can have only certain discrete energy values. As these isolated atoms are brought together to form a crystal, the electrons become restricted not to single energy levels, but rather to ranges of allowed energies, or bands called the valance and conduction bands (Figure 3-2). These two bands are separated by an energy band gap, which is a very important characteristic of the semiconductor material. At zero kelvin, all the electrons are confined to the valance band and the material is a perfect insulator. Above zero kelvin, some electrons have sufficient thermal energy to make a transition to the conduction band where they are free to move and conduct current through the crystal. The probability of an electron having enough energy to make the transition is given by the Fermi distribution function. The Fermi level shown on Figure 3-2 is the energy level at which the probability function is equal to one half. For pure semiconductors, the Fermi level is approximately in the center of the band gap. Note, though, that no electron actually has an energy of  $E_F$ , since they are not permitted to exist at energies in the band gap. The amount of energy required for an electron to move from the valance band to the

Table 3-1. Room-temperature properties of GaAs.

| Property                         | Parameter                               |

|----------------------------------|-----------------------------------------|

| Crystal structure                | Zinc blende                             |

| Lattice constant                 | 5.65 Å                                  |

| Density                          | 5.32 g/cm <sup>3</sup>                  |

| Atomic density                   | $4.5 \times 10^{22} \text{ atoms/cm}^3$ |

| Molecular weight                 | 144.64                                  |

| Bulk modulus                     | $7.55 \times 10^{11} \text{ dyn/cm}^2$  |

| Sheer modulus                    | $3.26 \times 10^{11} \text{ dyn/cm}^2$  |

| Coefficient of thermal expansion | $5.8 \times 10^{-6} \text{ K}^{-1}$     |

| Specific heat                    | 0.327 J/g-K                             |

| Lattice thermal conductivity     | 0.55 W/cm-°C                            |

| Dielectric constant              | 12.85                                   |

| Band gap                         | 1.42 eV                                 |

| Threshold field                  | 3.3 kV/cm                               |

| Peak drift velocity              | $2.1 \times 10^7 \text{ cm/s}$          |

| Electron mobility (undoped)      | 8500 cm <sup>2</sup> /V-s               |

| Hole mobility (undoped)          | 400 cm <sup>2</sup> /V-s                |

| Melting point                    | 1238°C                                  |

Figure 3-2. Energy band diagram for GaAs.

conduction band (energy band gap) depends on the temperature, the semiconductor material, and the material's purity and doping profile. For undoped GaAs, the energy band gap at room temperature is 1.42 eV. The energy band diagram is usually referenced to a potential called the vacuum potential. The electron affinity,  $q\chi$ , is the energy required to remove an electron from the bottom of the conduction band to the vacuum potential. For GaAs,  $q\chi$  is approximately 4.07 eV [2,3].

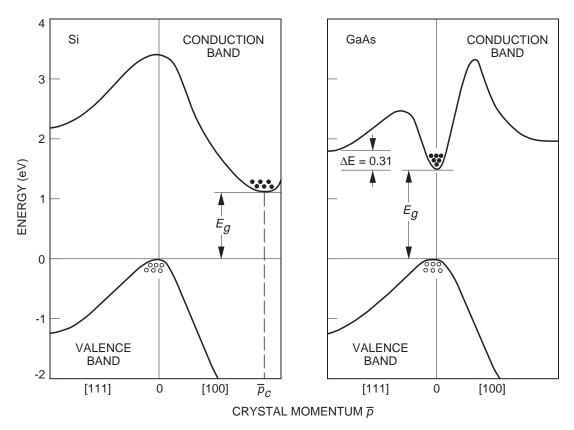

GaAs is a direct band gap semiconductor, which means that the minimum of the conduction band is directly over the maximum of the valance band (Figure 3-3). Transitions between the valance band and the conduction band require only a change in energy, and no change in momentum, unlike indirect band-gap semiconductors such as silicon (Si). This property makes GaAs a very useful material for the manufacture of light emitting diodes and semiconductor lasers, since a photon is emitted when an electron changes energy levels from the conduction band to the valance band.

Figure 3-3. Energy band structure of Si and GaAs.

Alternatively, an incident photon can excite an electron from the valence band to the conduction band, allowing GaAs to be used in photo detectors.

#### **B.** Mobility and Drift Velocity

GaAs has several advantages over silicon for operation in the microwave region—primarily, higher mobility and saturated drift velocity and the capability to produce devices on a semi-insulating substrate.

In a semiconductor, when a carrier (an electron) is subjected to an electric field, it will experience a force ( $\mathbf{F} = -q\mathbf{E}$ ) and will be accelerated along the field. During the time between collisions with other carrier ions and the semiconductor lattice, the carrier will achieve a velocity that is a function of the electric field strength. This velocity is defined as the drift velocity ( $\nu$ ). From the conservation of momentum, it can be shown that the drift velocity ( $\nu$ ) is proportional to the applied electric field (Figure 3-4) and can be expressed as

Figure 3-4. Drift velocity of electrons in GaAs and Si as a function of the electric field.

$$v = -\left(\frac{q\tau_c}{m^*}\right)\mathbf{E} \tag{3-1}$$

The proportionality factor depends on the mean free time between collisions ( $\tau_c$ ) and the electron effective mass ( $m^*$ ). The proportionality factor is called the electron mobility ( $\mu$ ) in units of cm<sup>2</sup>/V-s.

Mobility is an important parameter for carrier transport because it describes how strongly the motion of an electron is influenced by an applied electric field. From the equation above, it is evident that mobility is related directly to the mean free time between collisions, which in turn is determined primarily by lattice scattering and impurity scattering. Lattice scattering, which is a result of thermal vibrations of the lattice, increases with temperature and becomes dominant at high temperatures; therefore, the mobility decreases with increasing temperature. Impurity scattering on the other hand, which is a result of the movement of a carrier past an ionized dopant impurity, becomes less significant at higher temperatures [2].

Although the peak mobility of GaAs in the linear region can be as much as six times greater than that of silicon (Si) at typical field strengths, the advantage of GaAs may be only as much as a factor of two [4]. This still translates to the fact that GaAs devices can work at significantly higher frequencies than Si. The exact increase in the speed of operation depends on factors such as the circuit capacitance and the electric field regime in which the device operates.

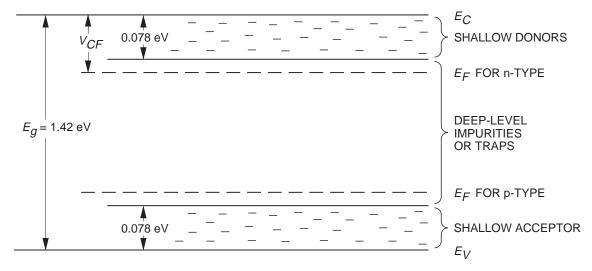

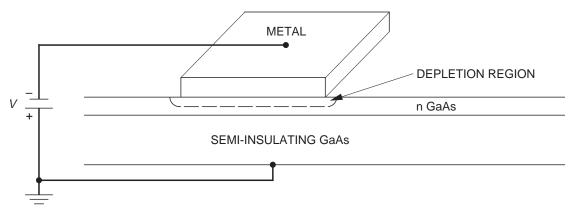

#### C. Semi-Insulating GaAs

The importance of semi-insulating GaAs is based on the fact that devices made of it by direct ion implantation are self-isolating, so that it is ideally suited to integrated circuit fabrication. Moreover, the semi-insulating substrate provides greatly reduced

parasitic capacitances, thus faster devices, and allows for integration and the implementation of monolithic microwave integrated circuits (MMIC).

Semi-insulating GaAs must meet the following requirements to provide semiconductor quality material:

- (1) Thermal stability during epitaxial growth or anneal of ion-implanted active layer.

- (2) Absence of undesirable substrate active layer interface effects, such as back-gating and light sensitivity.

- (3) No degradation of active layer properties by outdiffusion of impurities from substrate during thermal processing.

- (4) Lowest possible density of crystalline defects, such as dislocations, stacking faults, and precipitates.

To achieve some of these requirements, buffer layer technology was developed. A buffer layer is a relatively thick, high-resistivity epitaxial layer grown on the semi-insulating substrate. Another epitaxial layer is then grown on the buffer layer and used for the active layer. The buffer layer provides a physical barrier for undesirable substrate impurities and imperfections.

GaAs bulk resistivity can range from  $10^{-6}\,\Omega$ -cm to about  $10^{22}\,\Omega$ -cm, with the practical range being  $10^{-3}\,\Omega$ -cm to  $10^{8}\,\Omega$ -cm. This high resistivity is about six orders of magnitude greater than that of silicon and provides excellent isolation and substrate insulation. Undoped GaAs can be made semi-insulating by the addition of either oxygen or chromium to the melt. The resistivity of the semiconductor can be controlled by counter doping with a deep-level impurity that has a conductivity type opposite to that of the impurities introduced during growth.

#### D. Crystal Defects

No semiconductor crystalline material is perfect, and GaAs crystals, in spite of the efforts to control crystal growth, contain a number of crystal defects, dislocations, and impurities. These defects can have either desirable or undesirable effects on the electronic properties of GaAs. The natures of these defects and the observed effects are determined by the method of their incorporation into the material and the general growth conditions.

#### 1. Point Defects

Localized defects of atomic dimensions, called point defects, can occur in an otherwise perfect crystal lattice. These point defects can include vacancies, interstitials, misplaced atoms, intentionally introduced dopant impurities, and impurities introduced inadvertently during the material growth process. The study of point defects is important because of the effect these defects have on the electronic properties of the material and the strong relationship between diffusion and the number and type of defects in the crystalline material. The electrical properties of a semiconductor can be manipulated by the deliberate insertion of chemical defects (impurities) into the material during the growth and processing steps. However, intrinsic defects present in the material also play an important role in the electronic behavior of GaAs.

Many intrinsic defects are observed in GaAs. The concentration and effect of these defects are determined by the manner in which the material is grown. Intrinsic defects in GaAs include both arsenic and gallium vacancies, their concentration being determined by the overpressure of arsenic during processing. The effect of these vacancy defects has been observed to be neutral [5], deep donor-like, and deep acceptor-like [6].

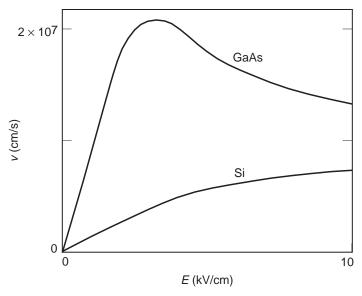

EL2, an important defect in GaAs, is present in material grown from an arsenic-rich melt. This defect is donor-like in character and is located at the middle of the energy gap [7]. It is thermally very stable and can withstand processing temperatures up to 900°C, and acts as an electron trap. The importance of this defect lies in its ability to convert p-type GaAs to semi-insulating material, and its thermal stability.

#### 2. Dislocations

A dislocation is a one-dimensional array of point defects in an otherwise perfect crystal. It occurs when the crystal is subjected to stresses in excess of the elastic limit of the material. Dislocations interact with chemical and other point defects. This interaction exists between the localized impurity atoms and the strain field in the vicinity of the dislocations. The presence of a dislocation is usually associated with an enhanced rate of impurity diffusion leading to the formation of diffusion pipes. This effect translates to the introduction of trapping states in the band gap, altering the etching properties of the wafer, and, most importantly, altering the electrical properties of the devices. Studies have shown detrimental effects of dislocations and dislocation densities on the source drain current and threshold voltage of field-effect transistors FETs [8,9], carrier concentration, and sheet resistance [10].

Dislocations generally are introduced as a result of a temperature gradient present during crystal growth. Modern crystal growth methods can routinely produce 7.6-cm (3-in.) wafers with dislocation densities of 10<sup>4</sup> to 10<sup>5</sup> cm<sup>-2</sup> for the Liquid Encapsulated Czochralski (LEC) and 8000 to 25,000 cm<sup>-2</sup> for Horizontal Bridgeman (HB) techniques.

#### 3. Impurities in GaAs

Chemical point defects (doping impurities) can be introduced to the crystalline material either deliberately or inadvertently as contamination during processing. In general, substitutional impurities are electronically active, whereas many contaminants are interstitial in nature and are electronically inactive. Dopants are classified as either donors or acceptors. A donor has one more electron than the atom it is replacing in the crystal. This extra electron is easily removed or donated to the conduction current. An acceptor, on the other hand, has one less electron than the atom it is replacing. Thus, an acceptor can easily capture an electron and prevent it from adding to the conduction current. Regardless of the type or character of the impurity, the electrical properties of the semiconductor are altered.

Figure 3-5 shows the energy band diagram of Figure 3-2 with the addition of impurities. Shallow donor or acceptor impurities have energy levels within 3kT of the conduction and valance band, respectively. Since the energy required for an electron to transition from these impurity energy levels to the nearest band edge is very small, they are typically fully ionized at room temperature. The Fermi level shifts from the band center towards the impurity levels to reflect this. In other words, for donor impurities, the Fermi level shifts towards the conduction band, and  $V_{CF}$  decreases as the donor doping concentration increases. A similar description can be made of acceptor impurities. It is

Figure 3-5. Energy band diagram of GaAs with impurities.

these shallow impurities that are used for doping purposes. Impurities with energies in the center of the band gap are called deep impurities. Deep impurities generally degrade device performance by reducing the carrier lifetime.

Both impurity types, deep and shallow, are present in GaAs in the form of complexes with gallium or arsenic. One of the most common is silicon. This group IV element can be used to give either p-type GaAs by incorporating it at low temperatures, or n-type GaAs by processing it at high temperatures. Another group IV element, carbon, is also used extensively to provide p-type GaAs. Chromium (Cr) behaves as an acceptor, with an impurity level close to the center of the energy gap. This property makes it very useful for counterdoping n-type GaAs to make it semi-insulating. Other elements such as copper, oxygen, selenium, and tin are also used in GaAs processing to provide the desired n- or p-like behavior.

# E. Thermal Characteristics

GaAs has a thermal conductivity of 0.55 W/cm-°C, which is about one-third that of silicon and one-tenth that of copper. As a consequence, the power handling capacity and therefore the packing density of a GaAs integrated circuit is limited by the thermal resistance of the substrate. The reliability of GaAs devices is directly related to the thermal characteristics of the device design, the mounting technique used for the die, and the materials used for that interface.

The thermal conductivity of GaAs is related to the temperature of the material over a wide temperature range and varies approximately as 1/T, where T is the temperature in kelvin. However, thermal conductivity can be considered linear over a very short temperature range [11].

The power handling capabilities, reliability, and performance of semiconductor devices are directly related to the junction temperature of the device during operation. While GaAs has a higher thermal resistivity than silicon, this is somewhat offset by the higher band gap of GaAs, allowing higher operating temperatures. Nevertheless, thermal considerations are extremely important in device design, packaging, and application.

#### References

- [1] H. Welker, Z. Naturforsch, Vol. A, No. 7, p. 744, 1952.

- [2] S. M. Sze, Semiconductor Devices Physics and Technology, J. Wiley, New York, 1985.

- [3] R. F. Pierret, *Semiconductor Fundamentals*, Addison-Wesley Publishing, New York, 1989.

- [4] R. Williams, *Modern GaAs Processing Methods*, Artech House, Dedham, MA, 1990.

- [5] H. C. Casey, "Diffusion in III-V Compound Semiconductors," *Atomic Diffusion in Semiconductors*, D. Shaw, Editor, Plenum, New York, 1973.

- [6] S. Y. Chiang, "Properties of Vacancy Defects in GaAs Single Crystals," *J. Appl. Phys.*, Vol. 45, p. 2986, 1975.

- [7] S. Markram-Ebied, "Nature of EL2: The Main Native Midgap Electron Trap in VPE and Bulk GaAs," in *Semi-insulating III-V Materials*, D. Look, Editor, Shiva Publishing Ltd., England, 1984.

- [8] Y. Nanishi, Jpn. J. Appl. Phys., Vol. 22, 1983.

- [9] S. Miyazawa, Appl. Phys. Lett., Vol. 44, 1984.

- [10] T. Honda, *Jpn. J. Appl. Phys.*, Vol. 22, 1983.

- [11] S. Wemple, "Thermal Design of Power GaAs," in *GaAs FET Principles and Technology*, J. DiLorenzo, Editor, Artech House, Dedham, MA., 1982.

# **Additional Reading**

Blakemore, J., "Semiconducting and Other Major Properties of Gallium Arsenide," *J. Appl. Phys.* Vol. 53, No. 10, October 1982.

### II. Metal-Semiconductor Junctions

G. E. Ponchak

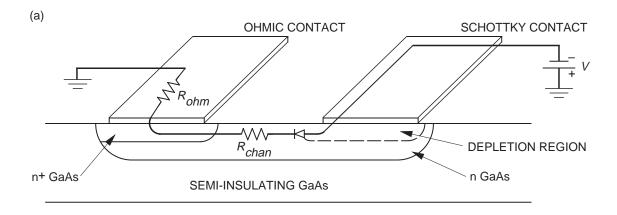

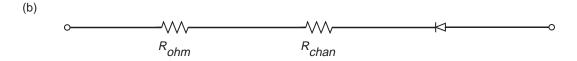

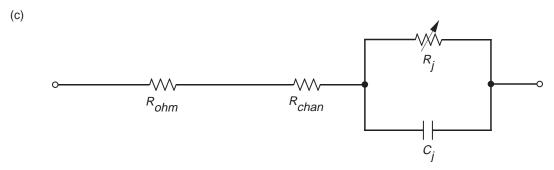

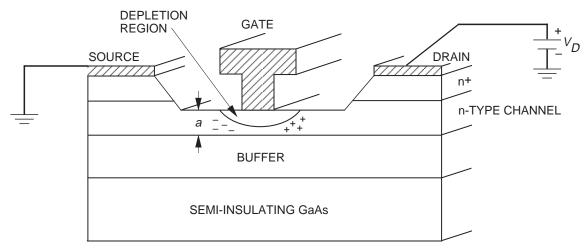

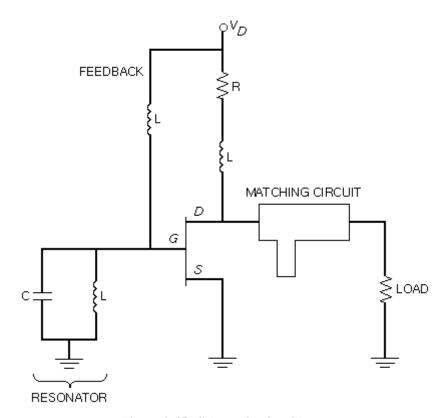

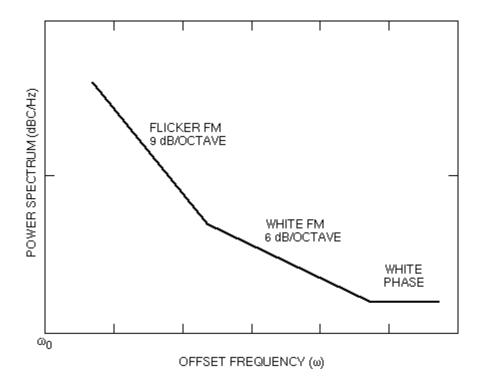

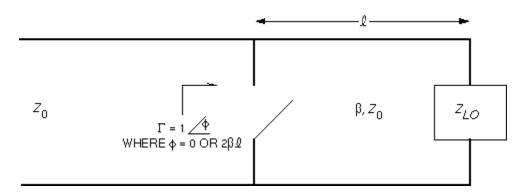

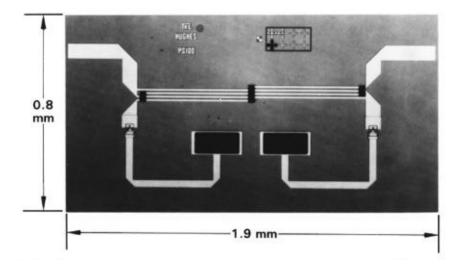

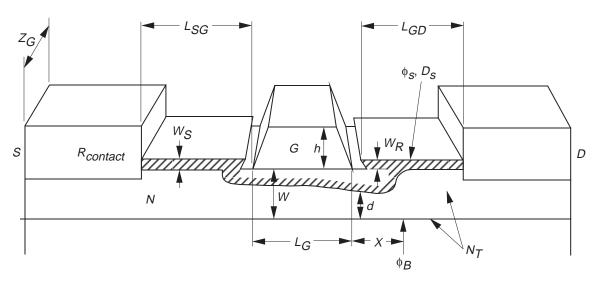

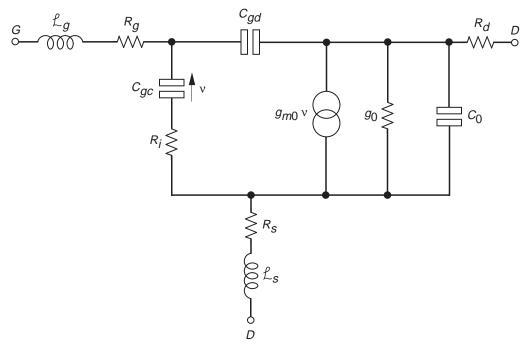

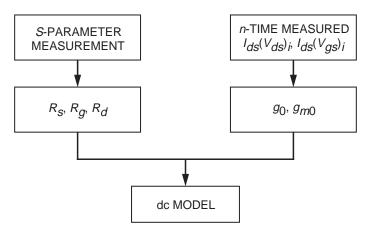

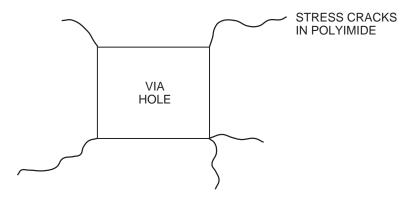

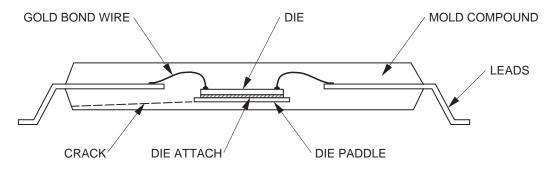

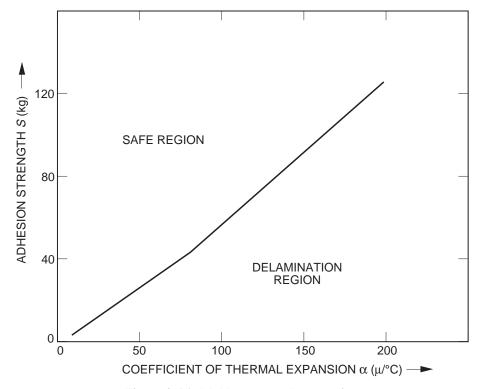

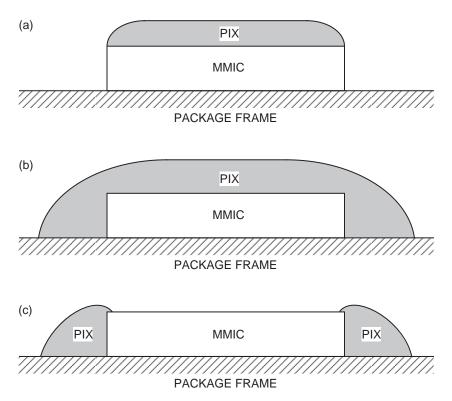

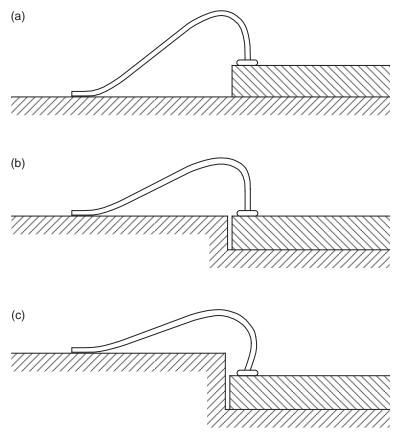

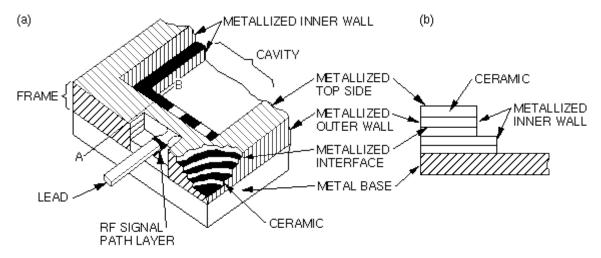

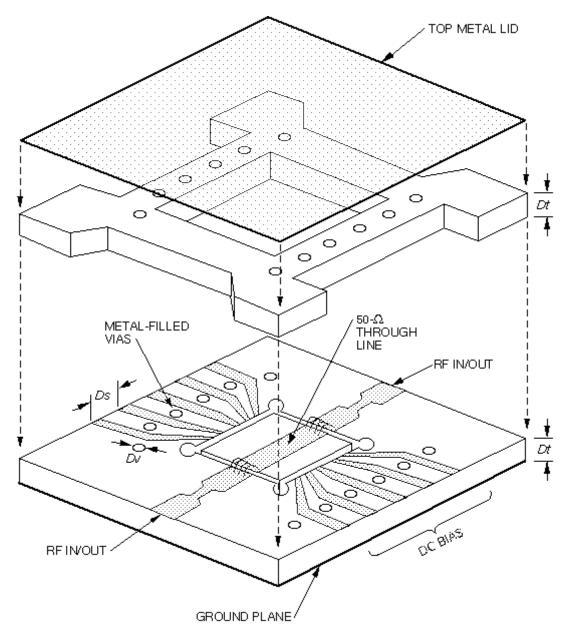

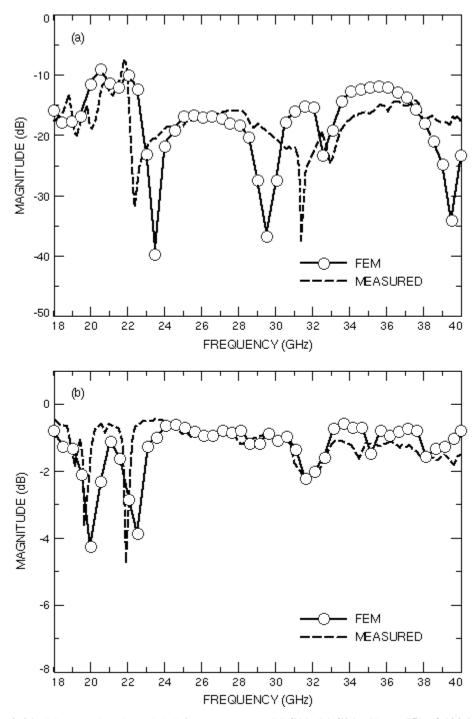

The earliest solid-state device was reported in 1874. It consisted of a wire tip pressed into a lead-sulfide crystal. This simple metal—semiconductor junction was the first solid-state device and became known as a whisker contact rectifier. Although whisker contact rectifiers are rarely used anymore, the metal—semiconductor junction is the most important solid-state component in microwave integrated circuits. A few examples of circuit elements that include metal—semiconductor junctions are Schottky diodes, varactor diodes, metal—semiconductor field-effect transistors (MESFETs), high-electron-mobility transistors (HEMTs), and heterojunction bipolar transistors (HBTs).